Webinar Series on

Webinar Series on

ANALOG VERIFICATION INSIGHTS

Writing UVM/SystemVerilog Testbenches for Analog/Mixed-Signal Verification

June 21, 2022 3:00 PM – 4:30 PM Pacific Time

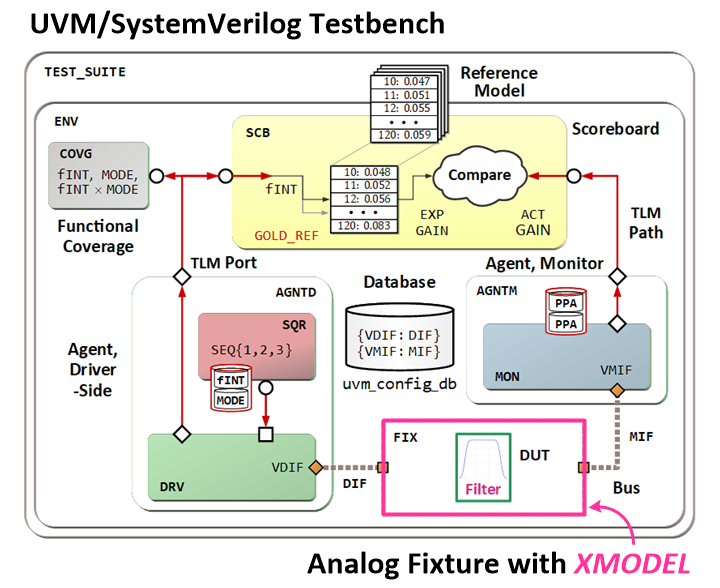

Learn how to write UVM testbenches for analog/mixed-signal circuits. UVM (Universal Verification Methodology) is a framework of standardized SystemVerilog classes to build reusable and scalable testbenches for digital designs, and it can be extended to verifying analog circuits simply by using a fixture module that generates analog stimuli and measures analog responses with Scientific Analog’s XMODEL.

Using a digitally-programmable audio bandpass filter as an example, we’ll show how to write a UVM testbench that measures the filter’s transfer gain at randomly-chosen frequencies, collects the results in a scoreboard until the desired coverage is met, and checks the supply current and bias voltages during power-down with assertions. The webinar will start with an intuitive yet systematic introduction to UVM.

Charles Dančak

University of California, San Diego | UCSD · Extension

Charles Dančak is a trainer and consultant based in Silicon Valley. He holds two MS degrees, one in electrical engineering and one in solid-state physics. Charles began his career as a technology engineer in one of Intel’s wafer fabs and spent ten years at Synopsys developing hands-on courses on HDL-based design, simulation, and DFT. He introduced the first SystemVerilog workshop in the University of California Extension system in 2007 and still teaches SystemVerilog online, currently with UC San Diego Extension (ECE-40301). Recently, Charles presented a paper on UVM for analog/mixed-signal verification at DVCon U.S. 2022.