Webinars

UVM Testbench for Verifying the Global Convergence of a DFE Adaptation Loop

35min

Jaeha Kim, “A UVM Testbench for Checking the Global Convergence of Analog/Mixed-Signal Systems: An Adaptive Decision-Feedback Equalizer Example”, Design and Verification Conference and Exhibition (DVCon) Europe, 2024.

Category: Webinars

Webinars

A UVM SystemVerilog Testbench for Directed & Random Testing of an AMS LDO Voltage Regulator

11min

Charles Dancak, “A UVM SystemVerilog Testbench for Directed & Random Testing of an AMS LDO Voltage Regulator”, Design and Verification Conference and Exhibition (DVCon) US, 2024.

Category: Webinars

Webinars

[5/5] UCIe PHY Modeling and Simulation with XMODEL

44min

This webinar presents the SystemVerilog models of a Universal Chiplet Interconnect Express (UCIe) interface, including both the analog circuits in the electrical layer and digital FSMs in the logical layer. The whole physical layer (PHY) model can be efficiently simulated in SystemVerilog, using Scientific Analog’s XMODEL.

Section 5: UCIe Logical Layer Modeling & Simulation

Category: Webinars

Webinars

[4/5] UCIe PHY Modeling and Simulation with XMODEL

35min

This webinar presents the SystemVerilog models of a Universal Chiplet Interconnect Express (UCIe) interface, including both the analog circuits in the electrical layer and digital FSMs in the logical layer. The whole physical layer (PHY) model can be efficiently simulated in SystemVerilog, using Scientific Analog’s XMODEL.

Section 4: UCIe Electrical Layer Modeling (Part 3: TX Datapath and RX)

Category: Webinars

Webinars

[3/5] UCIe PHY Modeling and Simulation with XMODEL

19min

This webinar presents the SystemVerilog models of a Universal Chiplet Interconnect Express (UCIe) interface, including both the analog circuits in the electrical layer and digital FSMs in the logical layer. The whole physical layer (PHY) model can be efficiently simulated in SystemVerilog, using Scientific Analog’s XMODEL.

Section 3: UCIe Electrical Layer Modeling (Part 2: TX Clock Path DLL & PI)

Category: Webinars

Webinars

[2/5] UCIe PHY Modeling and Simulation with XMODEL

29min

This webinar presents the SystemVerilog models of a Universal Chiplet Interconnect Express (UCIe) interface, including both the analog circuits in the electrical layer and digital FSMs in the logical layer. The whole physical layer (PHY) model can be efficiently simulated in SystemVerilog, using Scientific Analog’s XMODEL.

Section 2: UCIe Electrical Layer Modeling (Part 1: TX Clock Path PLL & DCC)

Category: Webinars

Webinars

[1/5] UCIe PHY Modeling and Simulation with XMODEL

25min

This webinar presents the SystemVerilog models of a Universal Chiplet Interconnect Express (UCIe) interface, including both the analog circuits in the electrical layer and digital FSMs in the logical layer. The whole physical layer (PHY) model can be efficiently simulated in SystemVerilog, using Scientific Analog’s XMODEL.

Section 1: UCIe Overview and Introduction to XMODEL

Category: Webinars

Tutorial

Low-Dropout (LDO) Regulator Modeling with XMODEL

16min

This video demonstrates how you can easily and effectively model the transient, DC, and AC characteristics of low-dropout regulators using XMODEL. This tutorial corresponds to the application note, ‘Low-Dropout Regulator Modeling with XMODEL’ located in the ‘Application Notes’ section of the Scientific Analog website.

Category: Tutorial

Webinars

[2/2] Harnessing the Power of UVM for AMS Verification with XMODEL

52min

This tutorial offers hands-on learning for writing UVM testbenches for analog/mixed-signal circuits. It will show that the framework of UVM can be extended to verifying analog circuits simply by using a well-defined fixture module encapsulating the device-under-verification (DUV) model and its AMS instrumentations described with XMODEL primitives.

Part 2

Category: Webinars

Webinars

[1/2] Harnessing the Power of UVM for AMS Verification with XMODEL

1h 40min

This tutorial offers hands-on learning for writing UVM testbenches for analog/mixed-signal circuits. It will show that the framework of UVM can be extended to verifying analog circuits simply by using a well-defined fixture module encapsulating the device-under-verification (DUV) model and its AMS instrumentations described with XMODEL primitives.

Part 1

Category: Webinars

Webinars

Writing UVM/SystemVerilog Testbenches for Analog/Mixed-Signal Verification

1h 37min

This webinar focuses on how to write UVM testbenches for analog/mixed-signal circuits. UVM (Universal Verification Methodology) is a framework of standardized SystemVerilog classes to build reusable and scalable testbenches for digital designs, and it can be extended to verifying analog circuits simply by using a fixture module that generates analog stimuli and measures analog responses with Scientific Analog’s XMODEL.

Category: Webinars

Webinars

Automatic Generation of SystemVerilog Models from Analog/Mixed-Signal Circuits: a Pipelined ADC Example

1h 15mins

The webinar addresses how to extract SystemVerilog models automatically from analog/mixed-signal circuits, and perform efficient verification of mixed-signal SoC’s using digital flows, such as UVM. It will introduce two modeling approaches, structural and functional, and demonstrate how these approaches work together using a pipelined analog-to-digital converter example.

Category: Webinars

Webinars

[9-10/10] Writing OOP-style SystemVerilog Testbench for Analog IPs

15min

This webinar addresses how to write an OOP-style SystemVerilog testbench for analog/mixed-signal circuits. The key testbench components such as the test sequence, driver, monitor, and scoreboard are presented in a step-by-step manner. Using a digitally-programmable analog filter as an example, this webinar discusses ways of reaching 100% functional coverage over the digital modes as well as analog inputs with random/directed tests and analog assertion checks.

Section 09: Environment Module

Section 10: OOP/XMODEL Guidelines

Category: Webinars

Webinars

[8/10] Writing OOP-style SystemVerilog Testbench for Analog IPs

10min

This webinar addresses how to write an OOP-style SystemVerilog testbench for analog/mixed-signal circuits. The key testbench components such as the test sequence, driver, monitor, and scoreboard are presented in a step-by-step manner. Using a digitally-programmable analog filter as an example, this webinar discusses ways of reaching 100% functional coverage over the digital modes as well as analog inputs with random/directed tests and analog assertion checks.

Section 08: Functional Coverage

Category: Webinars

Webinars

[7/10] Writing OOP-style SystemVerilog Testbench for Analog IPs

10min

This webinar addresses how to write an OOP-style SystemVerilog testbench for analog/mixed-signal circuits. The key testbench components such as the test sequence, driver, monitor, and scoreboard are presented in a step-by-step manner. Using a digitally-programmable analog filter as an example, this webinar discusses ways of reaching 100% functional coverage over the digital modes as well as analog inputs with random/directed tests and analog assertion checks.

Section 07: Analog Assertions

Category: Webinars

Webinars

[6/10] Writing OOP-style SystemVerilog Testbench for Analog IPs

6min

This webinar addresses how to write an OOP-style SystemVerilog testbench for analog/mixed-signal circuits. The key testbench components such as the test sequence, driver, monitor, and scoreboard are presented in a step-by-step manner. Using a digitally-programmable analog filter as an example, this webinar discusses ways of reaching 100% functional coverage over the digital modes as well as analog inputs with random/directed tests and analog assertion checks.

Section 06: Bypass/Power-Down

Category: Webinars

Webinars

[5/10] Writing OOP-style SystemVerilog Testbench for Analog IPs

8min

This webinar addresses how to write an OOP-style SystemVerilog testbench for analog/mixed-signal circuits. The key testbench components such as the test sequence, driver, monitor, and scoreboard are presented in a step-by-step manner. Using a digitally-programmable analog filter as an example, this webinar discusses ways of reaching 100% functional coverage over the digital modes as well as analog inputs with random/directed tests and analog assertion checks.

Section 05: The Scoreboard

Category: Webinars

Webinars

[4/10] Writing OOP-style SystemVerilog Testbench for Analog IPs

8min

This webinar addresses how to write an OOP-style SystemVerilog testbench for analog/mixed-signal circuits. The key testbench components such as the test sequence, driver, monitor, and scoreboard are presented in a step-by-step manner. Using a digitally-programmable analog filter as an example, this webinar discusses ways of reaching 100% functional coverage over the digital modes as well as analog inputs with random/directed tests and analog assertion checks.

Section 04: Driver and Monitor

Category: Webinars

Webinars

[3/10] Writing OOP-style SystemVerilog Testbench for Analog IPs

7min

This webinar addresses how to write an OOP-style SystemVerilog testbench for analog/mixed-signal circuits. The key testbench components such as the test sequence, driver, monitor, and scoreboard are presented in a step-by-step manner. Using a digitally-programmable analog filter as an example, this webinar discusses ways of reaching 100% functional coverage over the digital modes as well as analog inputs with random/directed tests and analog assertion checks.

Section 03: Sequence Component

Category: Webinars

Webinars

[2/10] Writing OOP-style SystemVerilog Testbench for Analog IPs

12min

This webinar addresses how to write an OOP-style SystemVerilog testbench for analog/mixed-signal circuits. The key testbench components such as the test sequence, driver, monitor, and scoreboard are presented in a step-by-step manner. Using a digitally-programmable analog filter as an example, this webinar discusses ways of reaching 100% functional coverage over the digital modes as well as analog inputs with random/directed tests and analog assertion checks.

Section 02: Fixture Subcircuits

Category: Webinars

Webinars

[1/10] Writing OOP-style SystemVerilog Testbench for Analog IPs

16min

This webinar addresses how to write an OOP-style SystemVerilog testbench for analog/mixed-signal circuits. The key testbench components such as the test sequence, driver, monitor, and scoreboard are presented in a step-by-step manner. Using a digitally-programmable analog filter as an example, this webinar discusses ways of reaching 100% functional coverage over the digital modes as well as analog inputs with random/directed tests and analog assertion checks.

Section 01: Testbench for Analog

Category: Webinars

Tutorial

Bottom-up Model Generation with MODELFIT

6min

This video demonstrates MODELFIT, a python library for fitting SPICE simulation data to XMODEL primitives. By leveraging the design expertise, the functional models produced by MODELFIT often provide faster speeds and higher accuracies.

Category: Tutorial

Tutorial

Bottom-up Model Generation with MODELZEN

8min

This video showcases how MODELZEN converts any SPICE netlist into an XMODEL netlist in SystemVerilog, using a continuous-time linear equalizer (CTLE) example. The extracted models run efficiently in SystemVerilog thanks to the event-driven simulation algorithm of XMODEL.

Category: Tutorial

Tutorial

Co-simulating XMODEL with SPICE

8min

This video demonstrates how to run a co-simulation between XMODEL and SPICE using a continuous-time linear equalizer (CTLE) example. GLISTER automatically prepares the co-simulation netlists and control files based on the hierarchy configuration and XMODEL works seamlessly with the host SystemVerilog simulator and SPICE simulator.

Category: Tutorial

Demo

GLISTER: graphical user interface for creating models

8min

This video gives introduction to GLISTER, a graphical user interface for creating analog circuit models. GLISTER lets you compose top-down models of your circuits in schematic forms by putting together the XMODEL primitive symbols.

Category: Demo

Demo

XMODEL vs Real-Number Verilog

15min

How is XMODEL different from Real-Number Verilog, which is another way of modeling analog circuits in SystemVerilog? This video highlights the key competitive advantages of XMODEL, which can run fast, event-driven simulation of analog circuits without sacrificing accuracy.

Category: Demo

Introduction

Modeling Silicon Photonic Systems with XMODEL

7min

Silicon photonic systems are fast emerging but also posing challenges to verification, as they integrate all the photonics, analog, and digital components in a single chip. Check out how the XMODEL’s event-driven simulation algorithm can be extended to handle such an impossible task.

Category: Introduction

Demo

Bottom-up Modeling of DC-DC Converter with MODELZEN

12min

This video demonstrates how one can automatically extract bottom-up models from a DC-DC regulator circuit using MODELZEN. With the extracted models, one can perform efficient verification of the circuits all in SystemVerilog.

Category: Demo

Demo

Bottom-up Modeling of Phase-Locked Loop with MODELZEN

12min

This video demonstrates how one can extract bottom-up models from a phase-locked loop circuit using MODELZEN. MODELZEN can extract either circuit-level models or functional models via the User-Defined Model (UDM) interface.

Category: Demo

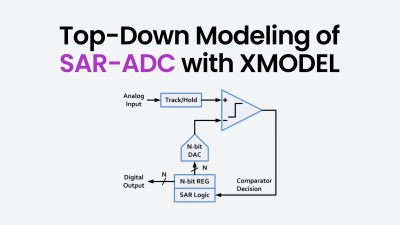

Demo

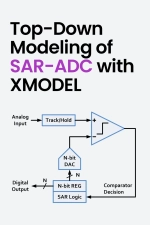

Top-Down Modeling of SAR-ADC with XMODEL

8min

A successive approximation register (SAR) ADC consists of an analog front-end and a digital finite-state machine and digitizes the analog input using a binary search algorithm. This video shows the top-down modeling of a SAR-ADC in XMODEL using GLISTER.

Category: Demo

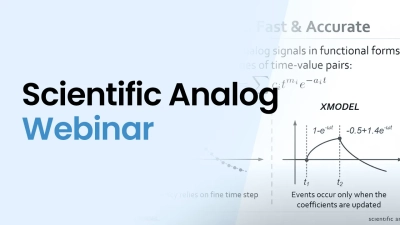

Introduction

Scientific Analog Webinar

37min

XMODEL offers the best way to verify analog circuits in SystemVerilog. XMODEL is a plug-in extension to a SystemVerilog simulator enabling fast and accurate analog/mixed-signal simulation with functional- and circuit-level models. GLISTER and MODELZEN are top-down and bottom-up modeling tools that make analog modeling a breeze.

Category: Introduction