Webinar Series on

Webinar Series on

ANALOG VERIFICATION INSIGHTS

Mixed-Signal Verification of Analog IP using SystemVerilog: An Object-Oriented Approach

June 25, 2021 12:00 PM – 1:30 PM PDT

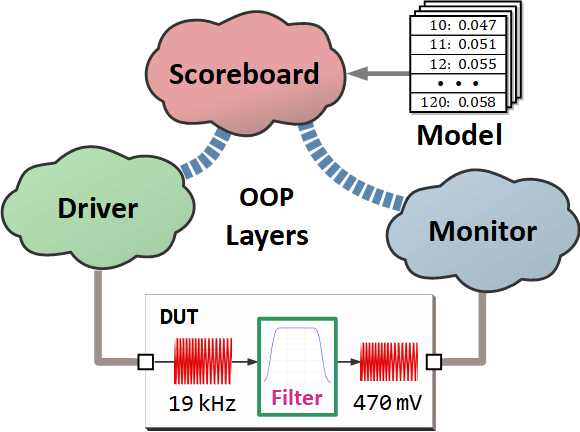

This webinar focuses on how to write a SystemVerilog OOP testbench to verify an analog/mixed-signal circuit controlled by digital logic. No language extensions like Verilog-AMS are used. The key testbench components are presented in a step-by-step manner, such as the test sequence, driver, monitor, and scoreboard. A few advanced OOP techniques, like randomizing a real-valued sine frequency, are introduced as well.

Using a digitally-programmable audio bandpass filter with power-down/bypass modes as an example, methods of reaching 100% functional coverage of both the digital modes and analog frequencies are examined. The testbench performs both the random and directed tests, and the analog assertions check the leakage current and bias voltage levels during the bypass and recovery mode, respectively. The scoreboard data reports voltage gains within 2% of SPICE over the filter’s entire passband.

Charles Dančak

University of California, San Diego | UCSD · Extension

Charles Dančak is a trainer and consultant based in Silicon Valley. He introduced the first SystemVerilog workshop in the University of California Extension system in 2007. Currently, he teaches SystemVerilog online, with UC San Diego Extension (ECE-40301). Charles began his career as a technology engineer in one of Intel’s wafer fabs and spent ten years at Synopsys in HDL-based design, simulation, and DFT. He has developed hands-on courses in HDL design and verification, nanometer ASIC flow, and DFT, and has taught them across North America, Europe and Asia.