Technical Paper

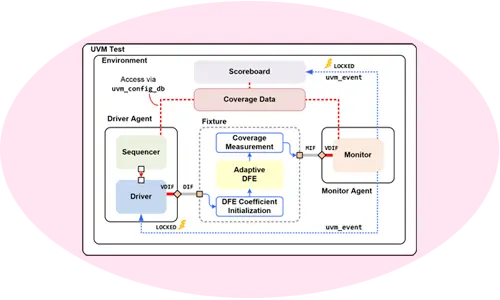

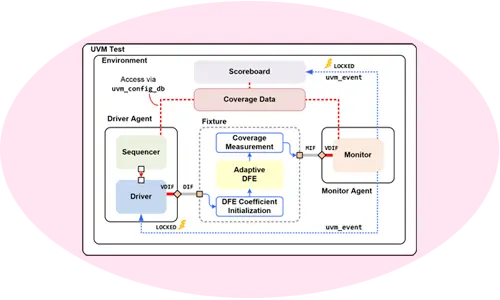

UVM testbench for verifying the global convergence of DFE adaptation loop

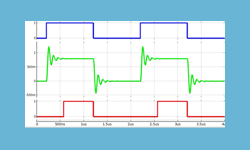

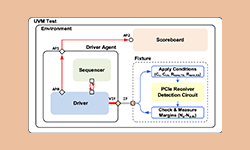

This UVM testbench checks whether a DFE adaptation loop always settles to the same final state regardless of the initial state.

This UVM testbench checks whether a DFE adaptation loop always settles to the same final state regardless of the initial state.

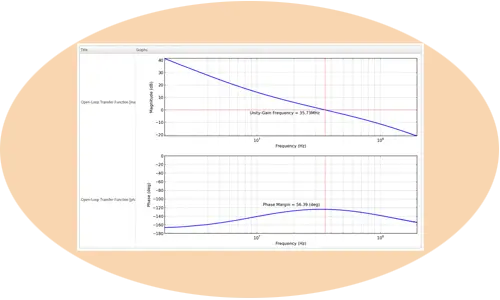

You can measure the open-loop transfer function of a PLL without breaking its feedback loop using a simplified Middlebrook method.

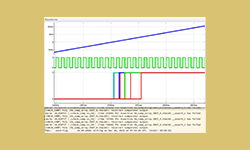

With this primitive, you can measure the frequency-domain transfer function of your circuit/model while running a time-domain simulation in SystemVerilog.

Season's Greetings, Checking a Clocked Comparator's Correct Output, and More

Checking the Settling of an Analog Signal, Handling Inherited Nets with Legacy SPICE Netlisters, and More

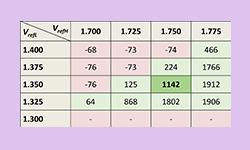

A UVM Testbench for Worst-Case Analysis Using Bayesian Optimization and More

XMODEL at DVCon Europe, Evaluating Transceivers with Multi-Drop Channels, and More

Modeling Variations in ReRAMs, Supporting RNM Nettypes, and More