TIP OF THE MONTH

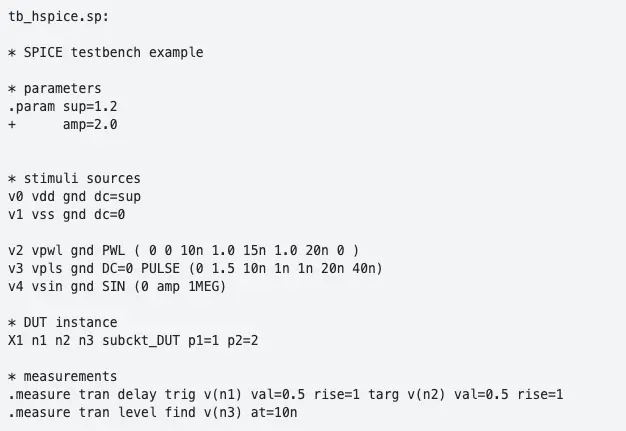

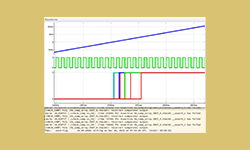

Translating HSPICE or Spectre testbenches into XMODEL’s equivalent testbenches

Find out how MODELZEN converts your SPICE testbenches including .MEASURE and .VEC statements to SystemVerilog testbenches.

TIP OF THE MONTH

Find out how MODELZEN converts your SPICE testbenches including .MEASURE and .VEC statements to SystemVerilog testbenches.

PRIMITIVE OF THE MONTH

These primitives are equivalent to a .IC statement in SPICE, which sets the initial condition of a node voltage or branch current.

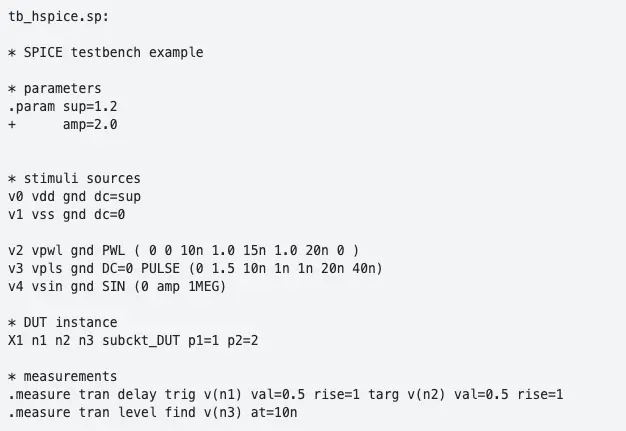

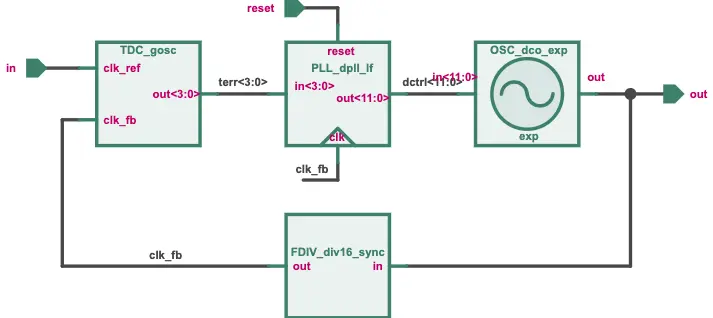

MODEL OF THE MONTH

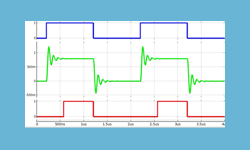

This example showcases how you can seamlessly combine the models for analog components and digital controller in SystemVerilog using XMODEL.

Season's Greetings, Checking a Clocked Comparator's Correct Output, and More

Checking the Settling of an Analog Signal, Handling Inherited Nets with Legacy SPICE Netlisters, and More

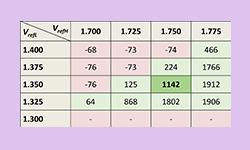

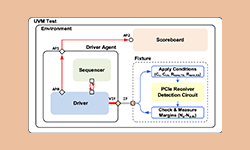

A UVM Testbench for Worst-Case Analysis Using Bayesian Optimization and More

XMODEL at DVCon Europe, Evaluating Transceivers with Multi-Drop Channels, and More

Modeling Variations in ReRAMs, Supporting RNM Nettypes, and More