New Tutorial

GLISTER Online Interactive Demo

Want to introduce GLISTER to your friends? This online interactive demo is easy and fun!

Want to introduce GLISTER to your friends? This online interactive demo is easy and fun!

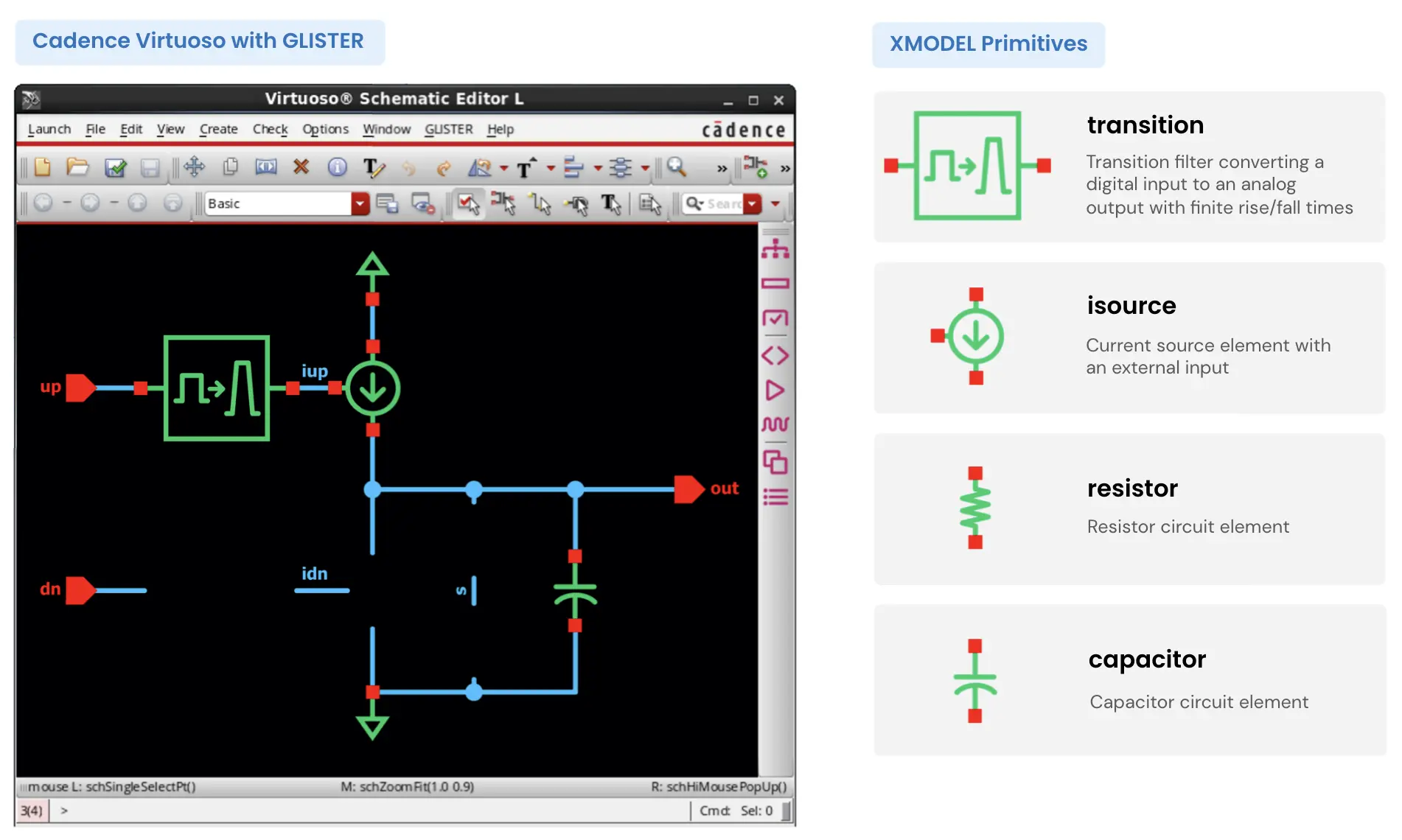

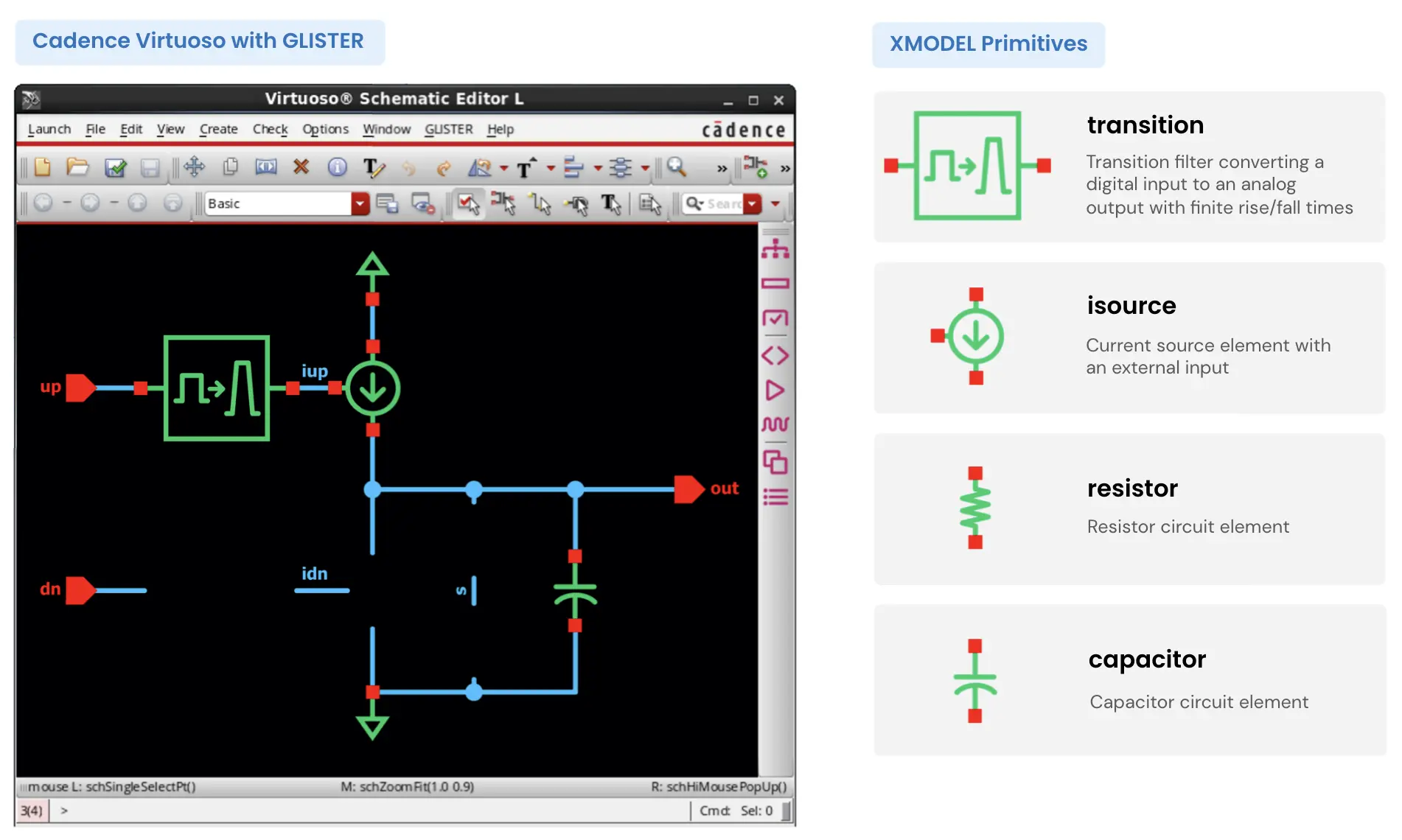

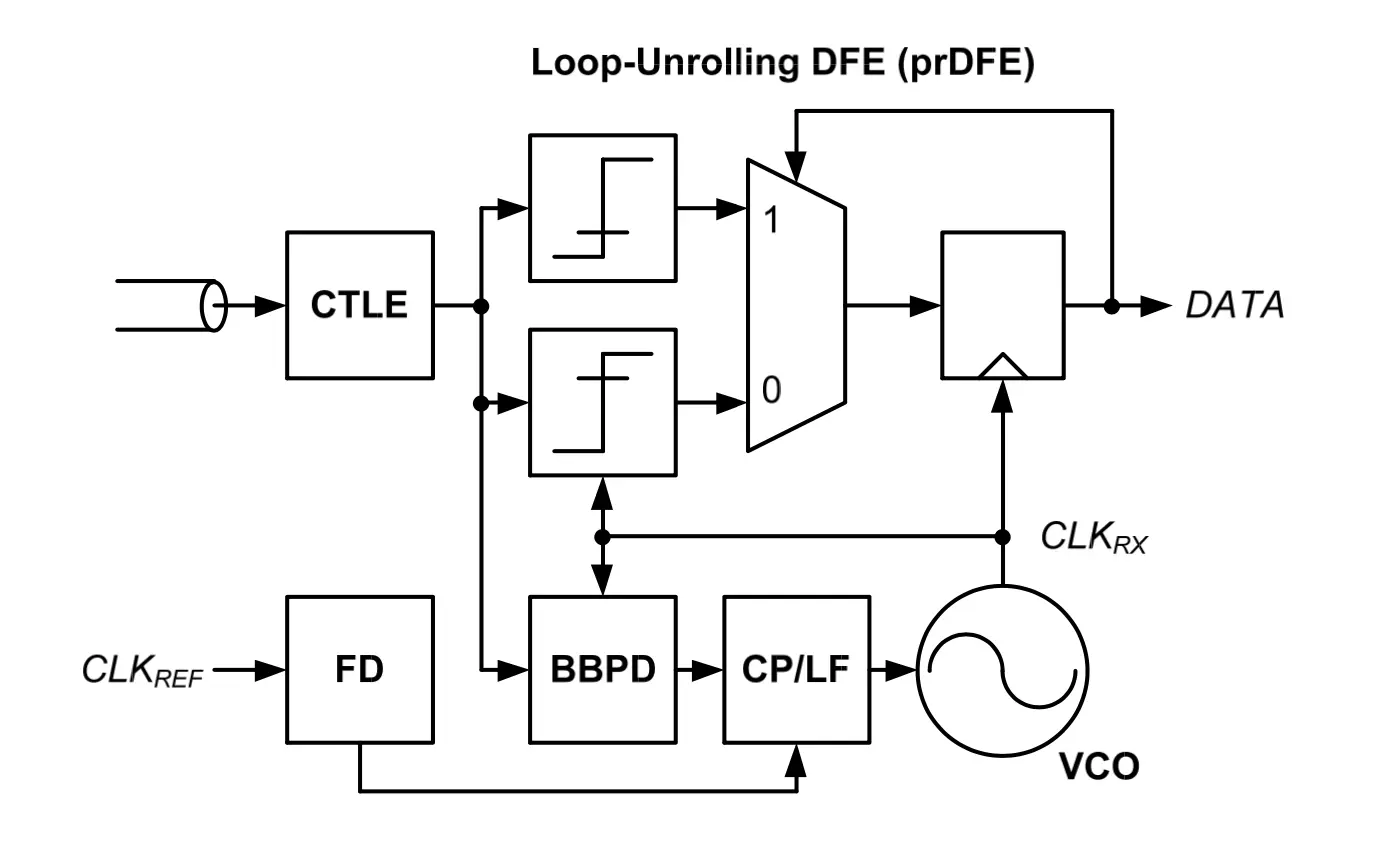

Check out this application note showcasing the model of a high-speed wireline receiver with CTLE/DFE equalization and half-rate bang-bang PLL-based CDR.

This primitive is the all time favorite, generating an xbit-type clock with optional sinusoidal jitter and random phase noise.

This release adds various improvements related to high-speed I/O modeling, such as the faster eye diagram plotting with XWAVE.

Season's Greetings, Checking a Clocked Comparator's Correct Output, and More

Checking the Settling of an Analog Signal, Handling Inherited Nets with Legacy SPICE Netlisters, and More

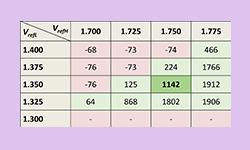

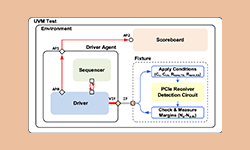

A UVM Testbench for Worst-Case Analysis Using Bayesian Optimization and More

XMODEL at DVCon Europe, Evaluating Transceivers with Multi-Drop Channels, and More

Modeling Variations in ReRAMs, Supporting RNM Nettypes, and More