TIP OF THE MONTH

How to generate and verify parallel streams of pseudo-random bits

Learn how to generate and verify parallel streams of pseudo-random digital bits using the 'prbs_gen' and 'probe_ber' primitives.

TIP OF THE MONTH

Learn how to generate and verify parallel streams of pseudo-random digital bits using the 'prbs_gen' and 'probe_ber' primitives.

PRIMITIVE OF THE MONTH

These primitives are handy when modeling passive R, L, C elements whose values change with inputs.

MODEL OF THE MONTH

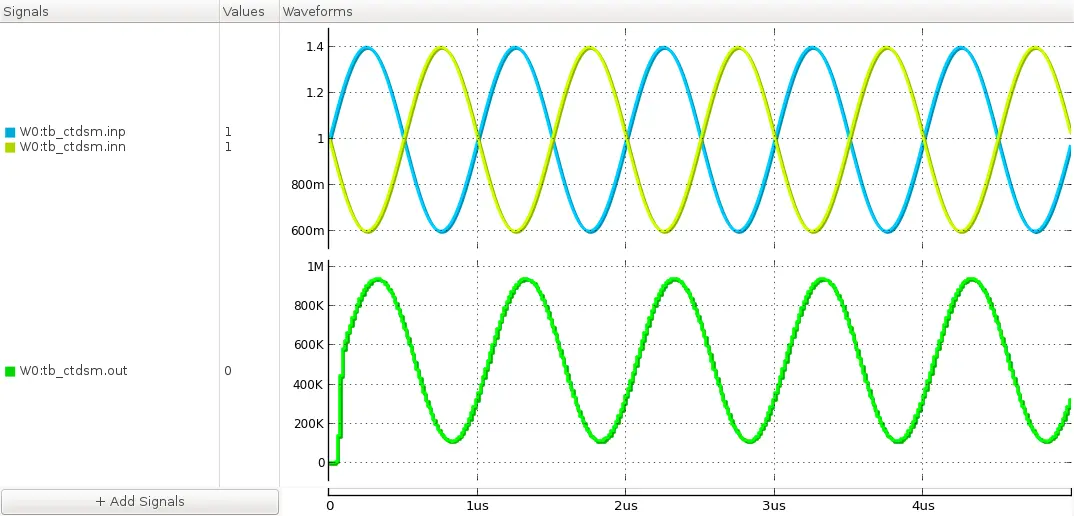

This example demonstrates how to model a switched-capacitor-based delta-sigma modulator (DSM) and simulate it along with a digital decimator in SystemVerilog.

Season's Greetings, Checking a Clocked Comparator's Correct Output, and More

Checking the Settling of an Analog Signal, Handling Inherited Nets with Legacy SPICE Netlisters, and More

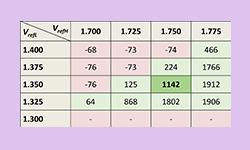

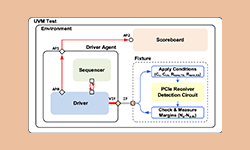

A UVM Testbench for Worst-Case Analysis Using Bayesian Optimization and More

XMODEL at DVCon Europe, Evaluating Transceivers with Multi-Drop Channels, and More

Modeling Variations in ReRAMs, Supporting RNM Nettypes, and More