Tip of the Month

Using PSL assertions for analog circuit checks

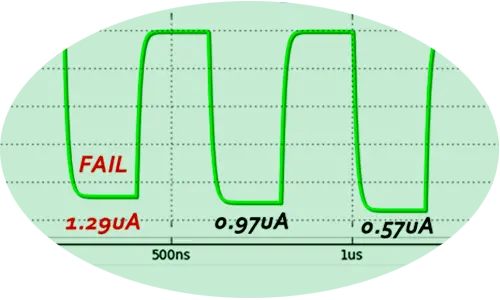

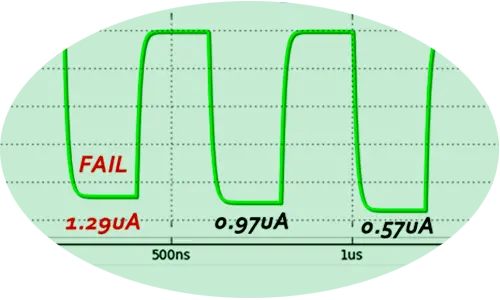

Here is an example of a PSL assertion checking the supply current level during a power-down mode.

Here is an example of a PSL assertion checking the supply current level during a power-down mode.

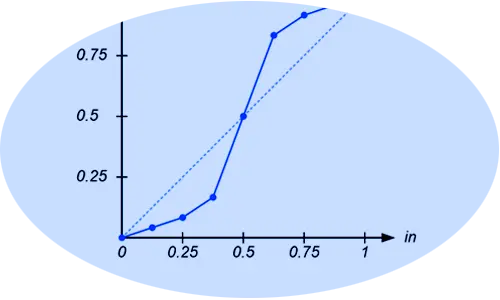

Adding nonlinear characteristics to the existing phase interpolator model is super easy. Just add a 'pwl_func' primitive.

This primitive is useful when checking whether an xreal-type signal is below a certain threshold over a time interval.

This release introduces an advanced circuit partitioning algorithm with 'vsource' elements, enabling efficient supply current simulations of large circuits.

Season's Greetings, Checking a Clocked Comparator's Correct Output, and More

Checking the Settling of an Analog Signal, Handling Inherited Nets with Legacy SPICE Netlisters, and More

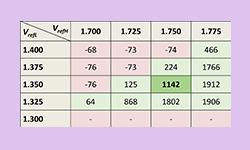

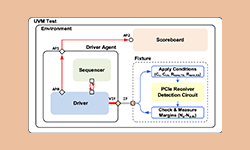

A UVM Testbench for Worst-Case Analysis Using Bayesian Optimization and More

XMODEL at DVCon Europe, Evaluating Transceivers with Multi-Drop Channels, and More

Modeling Variations in ReRAMs, Supporting RNM Nettypes, and More