Model of the Month

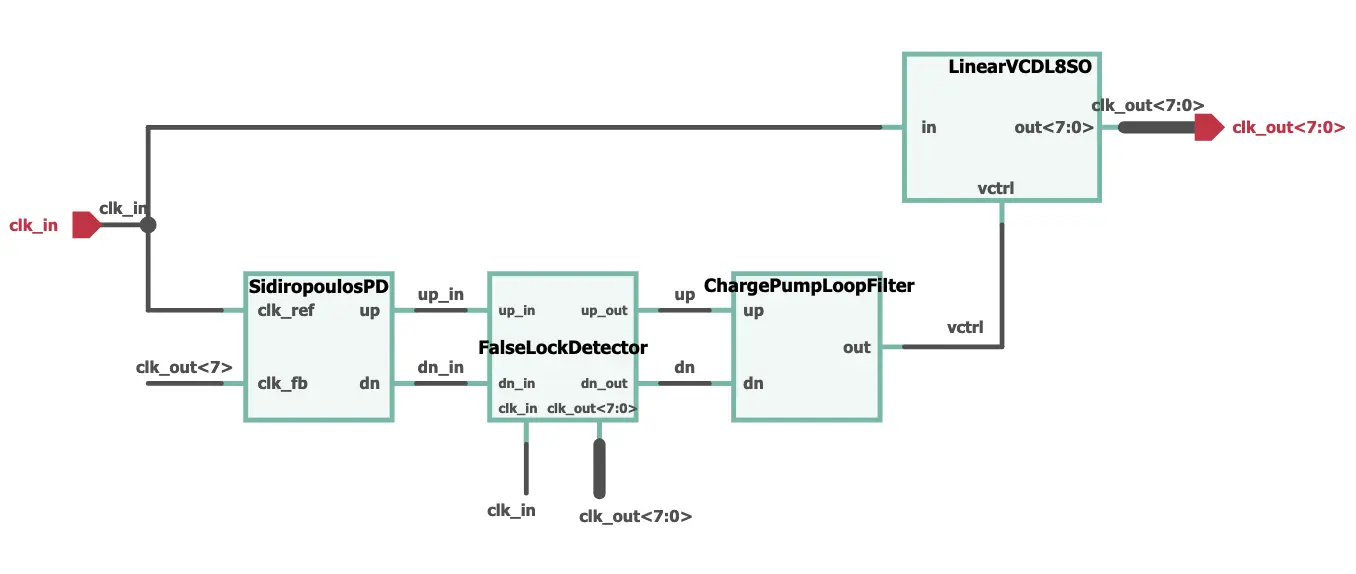

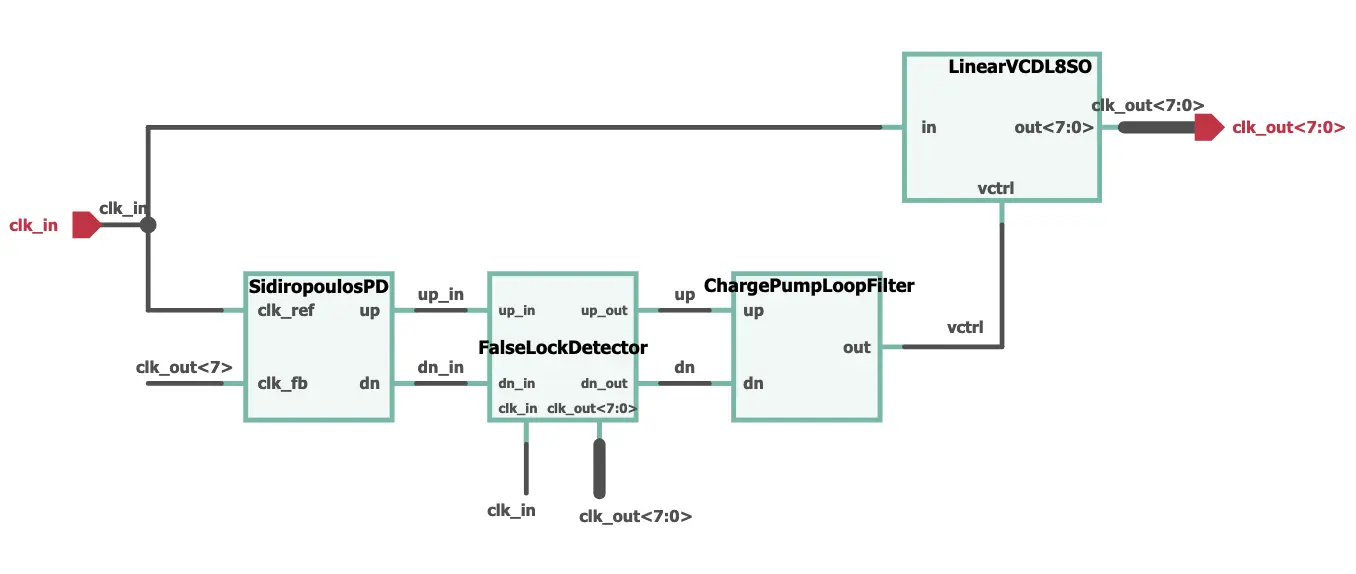

Delay-locked loop with false-lock detector

This model describes a delay-locked loop (DLL) that can recover from false-lock conditions. It is modeled after the DLL published by S. Byun, et al. in 2003.

This model describes a delay-locked loop (DLL) that can recover from false-lock conditions. It is modeled after the DLL published by S. Byun, et al. in 2003.

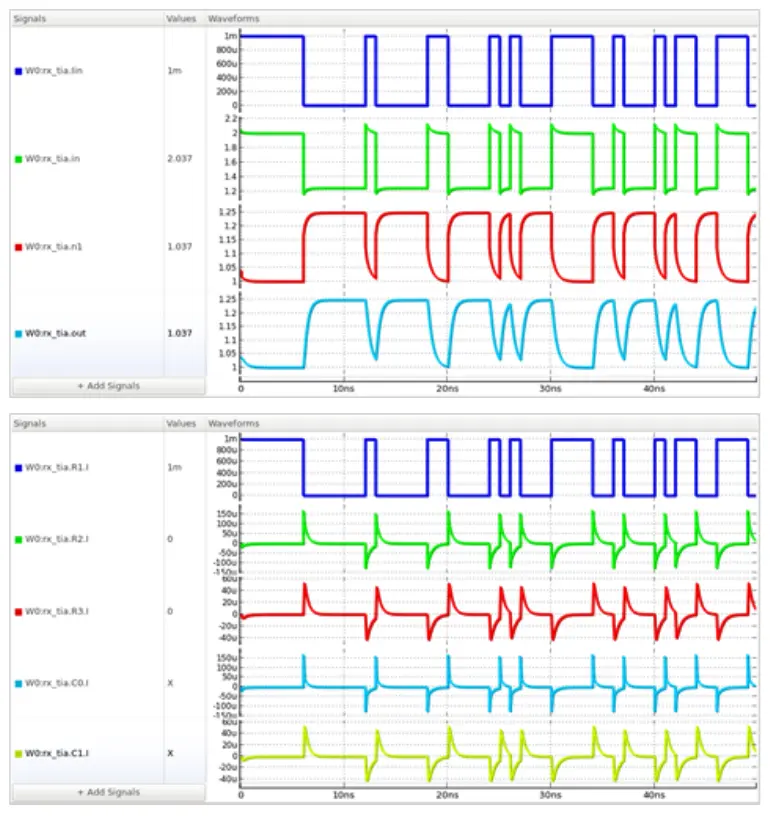

Learn more about the XMODEL's capability of simulating both the voltage and current waveforms of circuit-level models.

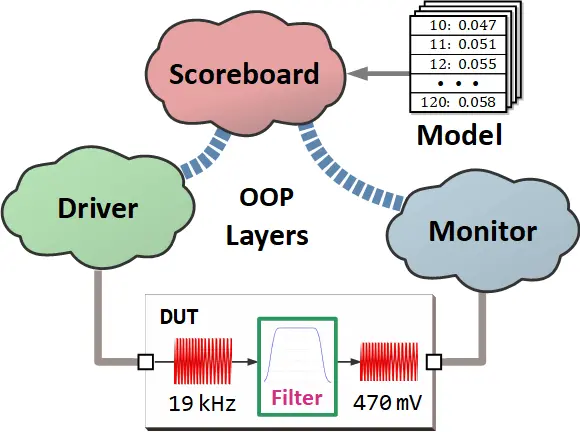

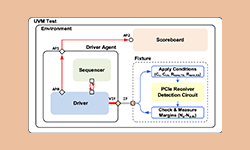

Join this webinar on how to write an OOP-style SystemVerilog testbench for analog/mixed-signal circuits, performing random and directed tests with analog assertion checks.

Season's Greetings, Checking a Clocked Comparator's Correct Output, and More

Checking the Settling of an Analog Signal, Handling Inherited Nets with Legacy SPICE Netlisters, and More

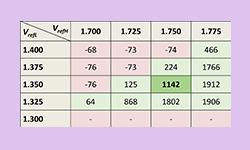

A UVM Testbench for Worst-Case Analysis Using Bayesian Optimization and More

XMODEL at DVCon Europe, Evaluating Transceivers with Multi-Drop Channels, and More

Modeling Variations in ReRAMs, Supporting RNM Nettypes, and More