Model of the Month

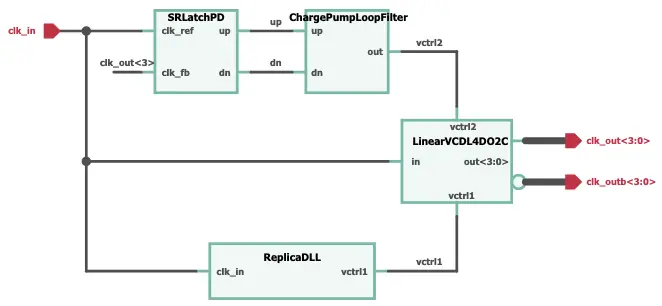

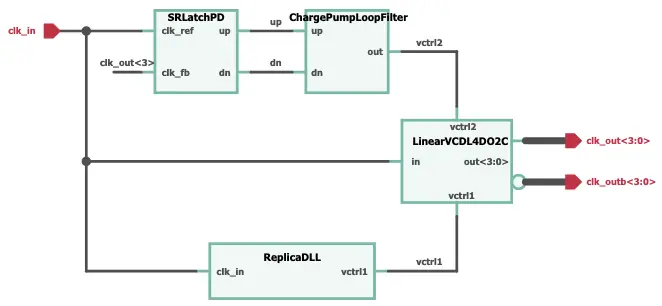

DLL with a replica loop

Check out this model for a delay-locked loop (DLL) that operates over a wide frequency range without false locks using a replica loop, published by Y. Moon, et al. in 2000.

Check out this model for a delay-locked loop (DLL) that operates over a wide frequency range without false locks using a replica loop, published by Y. Moon, et al. in 2000.

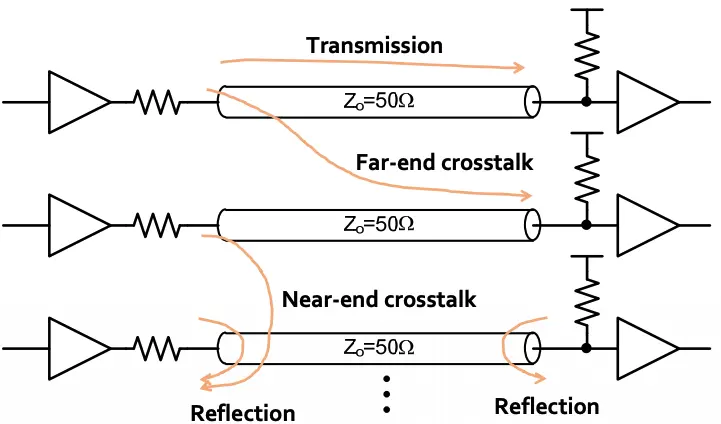

With the new 'sparam_to_tline' utility, you can now extract a multi-port transmission line model including all the port-to-port transfer functions such as reflections and crosstalks from an S-parameter file.

This primitive models a D-flipflop, with optional setup and hold time violation checks.

This release adds the support for UDM mappings on individual slices of parallel instances, and internal current probing for variable RLC and switch primitives.

Season's Greetings, Checking a Clocked Comparator's Correct Output, and More

Checking the Settling of an Analog Signal, Handling Inherited Nets with Legacy SPICE Netlisters, and More

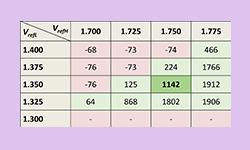

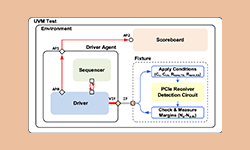

A UVM Testbench for Worst-Case Analysis Using Bayesian Optimization and More

XMODEL at DVCon Europe, Evaluating Transceivers with Multi-Drop Channels, and More

Modeling Variations in ReRAMs, Supporting RNM Nettypes, and More