Upcoming Tutorial

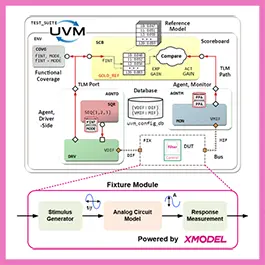

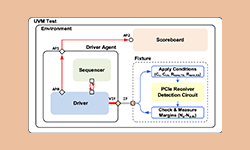

Harnessing the Power of UVM for AMS Verification with XMODEL

Don't miss the opportunity to join this 3-hour hands-on tutorial at DVCon US 2023 and learn how to write UVM testbenches for analog/mixed-signal circuits!

Don't miss the opportunity to join this 3-hour hands-on tutorial at DVCon US 2023 and learn how to write UVM testbenches for analog/mixed-signal circuits!

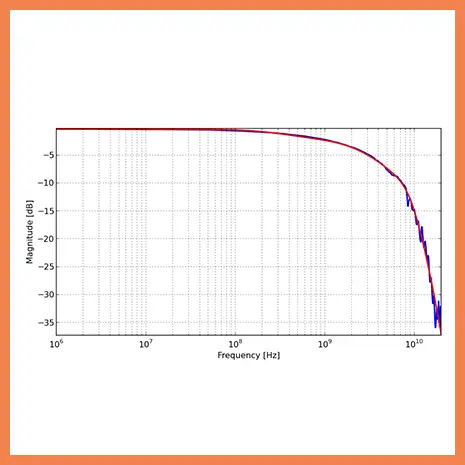

Want to simulate your high-speed transceiver model while gradually varying the frequency-dependent loss of the channel? Here is a simple tip on how.

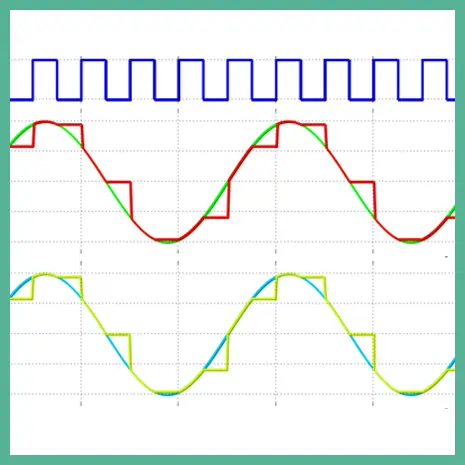

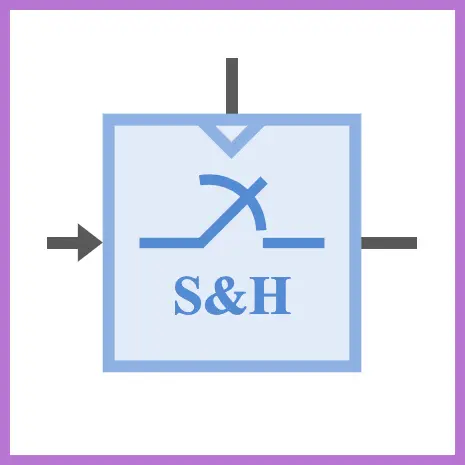

Check out these two simple ways of modeling a track-and-hold circuit.

This primitive models a sample-and-hold circuit, sampling the input at the clock's triggering edge and holding it til the next edge.

Season's Greetings, Checking a Clocked Comparator's Correct Output, and More

Checking the Settling of an Analog Signal, Handling Inherited Nets with Legacy SPICE Netlisters, and More

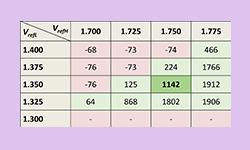

A UVM Testbench for Worst-Case Analysis Using Bayesian Optimization and More

XMODEL at DVCon Europe, Evaluating Transceivers with Multi-Drop Channels, and More

Modeling Variations in ReRAMs, Supporting RNM Nettypes, and More