Tutorial Updates

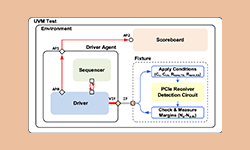

Modeling and simulation of high-speed I/O interfaces with XMODEL

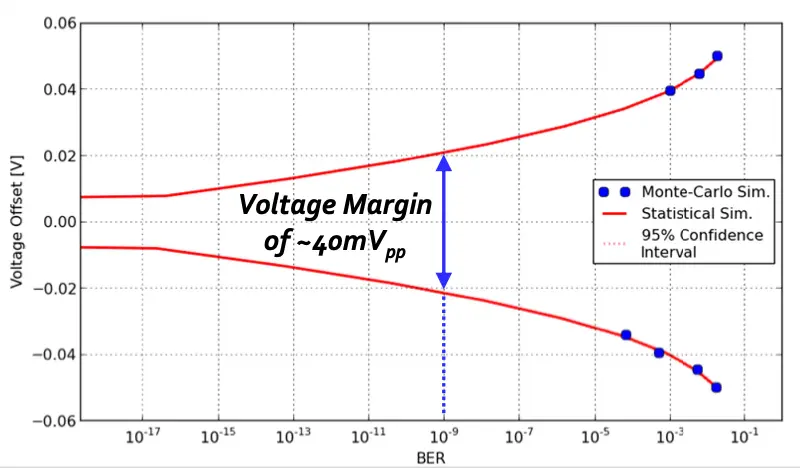

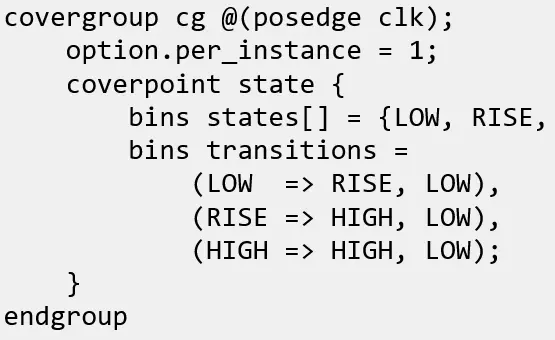

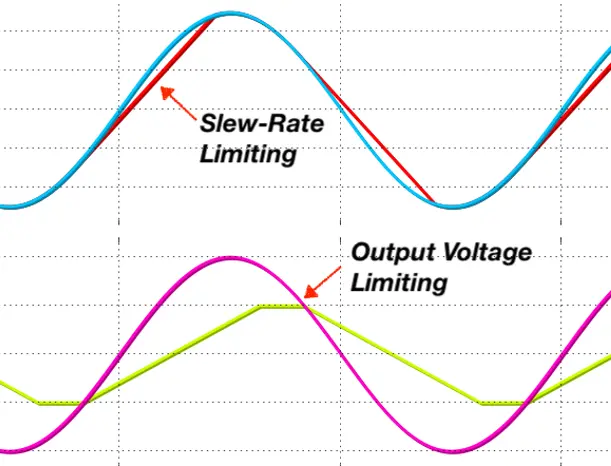

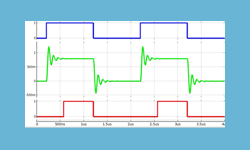

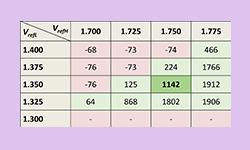

This popular tutorial is now updated with channel crosstalk modeling, voltage-mode transmit equalizer, dither suppression in bang-bang CDRs, and new scripts for BER bathtub, JTRAN, and JTOL simulations.