Webinar Series on

Webinar Series on

ANALOG VERIFICATION INSIGHTS

UCIe PHY Modeling and Simulation with XMODEL

June 29, 2023 14:00 – 15:30 PM Pacific Time

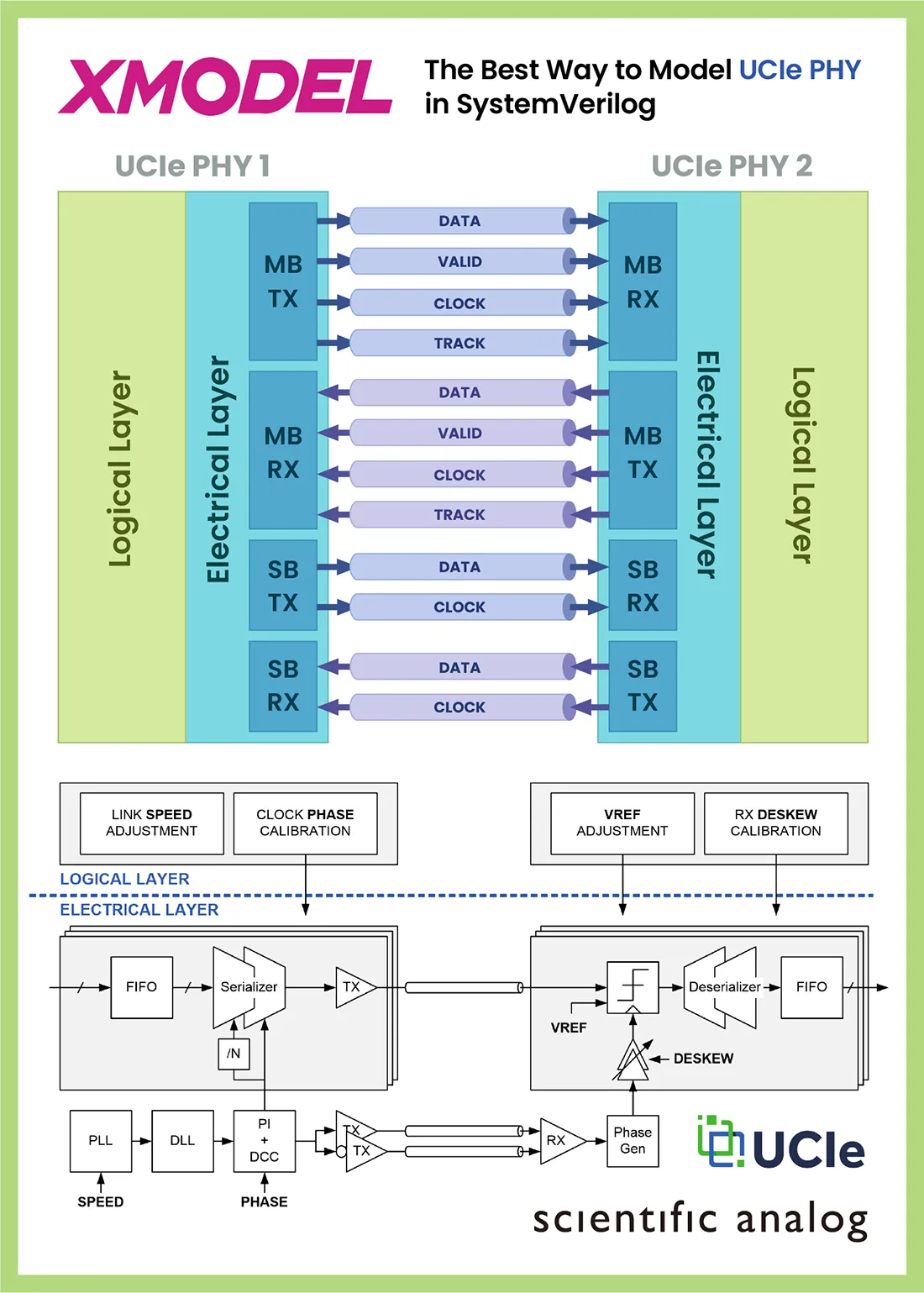

Chiplets are emerging as a new way of building IC systems via heterogeneous integration, and Universal Chip Interconnect Express (UCIe) is one of the standards defining the interconnects among chiplets. This webinar presents the SystemVerilog models of a Universal Chiplet Interconnect Express (UCIe) interface, including both the analog circuits in the electrical layer and digital FSMs in the logical layer. The whole physical layer (PHY) model can be efficiently simulated in SystemVerilog, using Scientific Analog’s XMODEL.

This webinar is organized in two parts. The first part gives a brief overview of the UCIe standard and explains why XMODEL is the best way to model and verify UCIe PHY, especially considering the close interactions between its electrical layer and logical layer. It will show how to model various analog circuits in the electrical layer, including the phase-locked loop (PLL), delay-locked loop (DLL), duty-cycle corrector, phase interpolator, and transmitter/receiver circuits. Each circuit block is modeled using XMODEL primitives, which enable fast and accurate simulation of their analog behaviors in SystemVerilog.

The second part shows how you can design the finite-state machines (FSMs) in the logical layer, performing digital training and calibrations on the reference voltage levels, clock-to-data timing, lane-to-lane skews, and link data rate via a series of data transmission tests with pseudo-random bit sequences. All the FSMs are described in SystemVerilog, and with XMODEL, you can simulate this logical layer model interacting with the electrical layer model entirely in SystemVerilog. It implies that you can also use various features of SystemVerilog to check the thoroughness of your simulation, such as checking the FSM state coverage.

This webinar will be beneficial to everyone who is interested in the design and verification of UCIe PHY. For analog circuit designers, the presented models will help understand the requirements posed on each circuit block, such as the scaling of bandwidth to support a wide range of data rates from 4GT/s to 32GT/s. For digital verification engineers, the presented testbenches will show how to perform SystemVerilog-based verification on the systems containing analog circuits. And most importantly, by running the simulations with the provided models, you can gain a hands-on understanding on how the various components of a UCIe PHY work to realize a high-bandwidth interconnect between chiplets.

Jaeha Kim

C.E.O. & Founder, Scientific Analog, Inc., Palo Alto, CA / Professor, Seoul National University, Korea

Jaeha Kim is CEO and founder of Scientific Analog, Inc., Palo Alto, CA and Professor at Seoul National University (SNU), Seoul, Korea. With a flagship product called XMODEL, he is pursuing ways to make analog design and verification as efficient as digital. Dr. Kim received the B.S. degree from SNU in 1997, and the M.S. and Ph.D. degrees from Stanford University in 1999 and 2003, respectively. Prior to joining SNU, Dr. Kim was with Stanford University as Acting Assistant Professor and with Rambus, Inc. as Principal Engineer. Prof. Kim is a recipient of the Takuo Sugano award for Outstanding Far-East Paper at 2005 ISSCC and is cited as Top 100 Technology Leader of Korea by the National Academy of Engineering of Korea in 2020.