PDC_XorGatePD : A phase-only detector with an exclusive-OR gate

A phase-only detector measures the phase difference between two input clocks, clk_ref and clk_fb and expresses the result with the pulsewidths of the two outputs up and dn. This particular PD is based on an exclusive-OR (XOR) gate, which toggles its outputs whenever one of the input clocks switches. Assuming the input clocks with 50% duty-cycles, the net pulsewidth difference between the up and dn outputs becomes zero when the phase difference between the two clocks is pi/2 radians. However, one of the drawbacks of this XOR-gate PD is that its locking point may change as the duty-cycles of the input clocks deviate from 50%.

The model is described using the gate primitives such as xor_xbit, inv_xbit, and buf_xbit to process accurate timings of digital pulses without being limited by the simulation timstep.

Input/Output Terminals

| Name | I/O | Type | Description |

| dn | output | xbit | dn output |

| up | output | xbit | up output |

| clk_fb | input | xbit | feedback clock |

| clk_ref | input | xbit | reference clock |

List of Testbenches

| tb_check : A testbench for checking the basic operation of a phase detector (PD) |

| tb_meas_tfdc : A testbench for measuring the phase error vs. net output pulsewidth transfer characteristics of a phase detector (PD) |

tb_check : A testbench for checking the basic operation of a phase detector (PD)

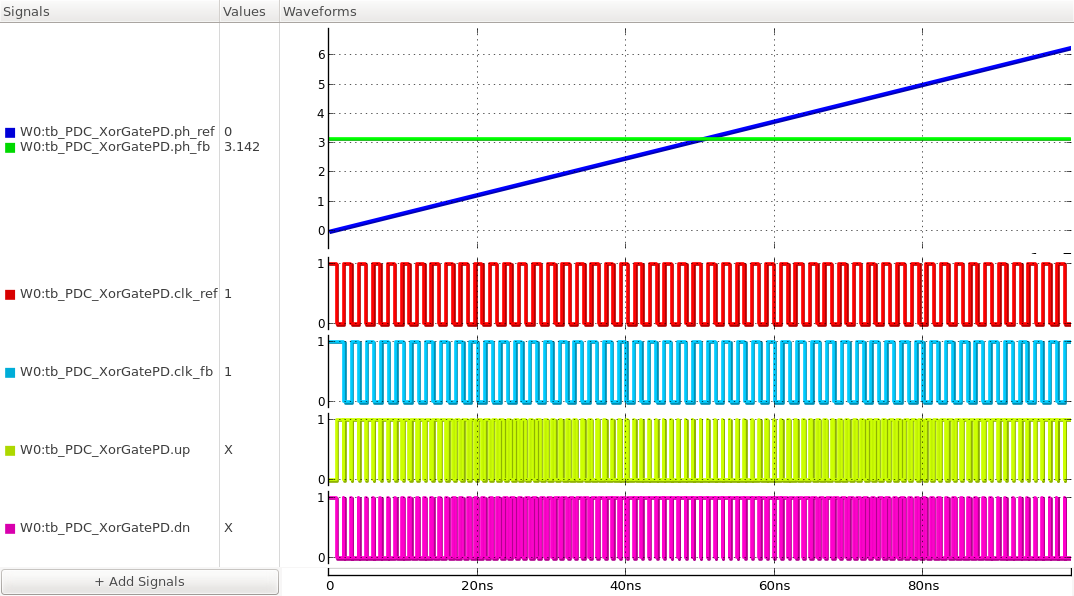

This testbench checks the basic functionality of a phase detector (PD) by applying the equal-frequency clocks to its inputs clk_ref and clk_fb, of which phase difference gradually varies from -pi to +pi radians. The net pulsewidth of the PD outputs up and dn indicates the timing difference between the two input clocks.

Simulation Results

Figure. input and output waveforms.

tb_meas_tfdc : A testbench for measuring the phase error vs. net output pulsewidth transfer characteristics of a phase detector (PD)

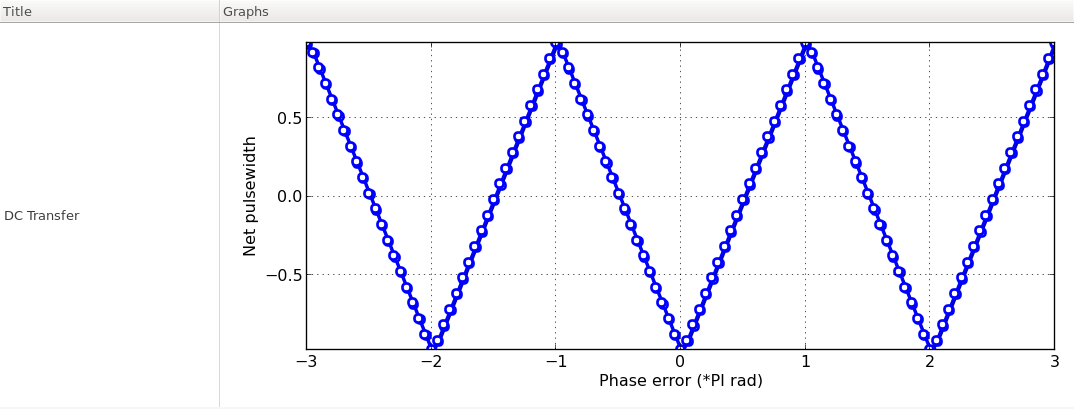

This testbench measures the phase error vs. net output pulsewidth transfer characteristics of a phase detector (PD). The testbench is configured with a probe_dc primitive, which gradually varies the phase difference between the two input clocks clk_ref and clk_fb from -3*pi to 3*pi radians and measures the net pulsewidth difference between the outputs up and dn.

A phase-only detector (PD) is expected to exhibit a transfer characteristic of which net output pulsewidth scales linearly with the phase error.

Simulation Results

Figure. input-to-output transfer characteristics of the phase detector.