DIV_AsyncDividerBy16 : An asynchronous divide-by-16 frequency divider

A frequency divider produces an output clock with a frequency that is equal to a divided value of the input clock frequency. An asynchronous frequency divider can be realized as a ripple-carry adder based counter, such as a chain of toggle flip-flops. Since each toggle flip-flop adds a clock-to-q delay, the final output clock out may not be well synchronized to the input clock with a known timing relationship. This long, uncertain latency between the input and output of the frequency divider may be undesirable in some timing-sensitive, low-noise applications.

This model describes an asynchronous divide-by-16 frequency divider as a chain of four toggle flip-flops. The parameter delay_cq defines the clock-to-q delay of each toggle flip-flop.

Input/Output Terminals

| Name | I/O | Type | Description |

| out | output | xbit | divided output clock |

| in | input | xbit | input clock |

Parameters

| Name | Type | Default | Description |

| delay_cq | real | 40p | clk-to-q delay of each flip-flop |

List of Children Cells

| BLK_ToggleFF : A toggle flip-flop (T-FF) |

List of Testbenches

| tb_check : A testbench for checking the basic operation of a frequency divider with a fixed-frequency clock input |

tb_check : A testbench for checking the basic operation of a frequency divider with a fixed-frequency clock input

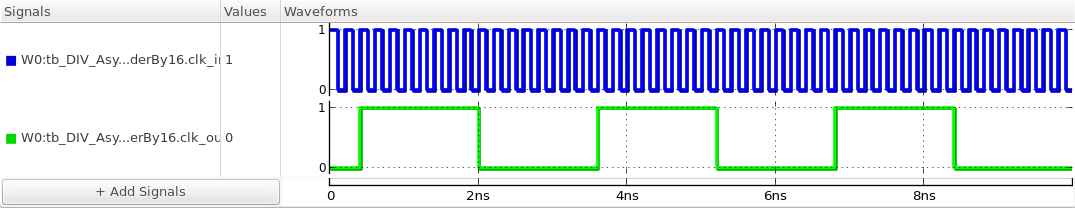

The testbench checks the basic functionality of a frequency divider by applying a fixed-frequency clock to its input in. The frequency divider is expected to produce an output clock of which frequency is a divided value of the input frequency.

Simulation Results

Figure. input and output waveforms.