BLK_DelayElement2C : A variable delay element with dual control inputs and linear V-to-D characteristics

A variable delay element propagates an input clock in to an output clock out with a variable amount of delay.

In this particular model, the delay is controlled by two control voltages vctrl1 and vctrl2 via linear V-to-D characteristics. That is:

delay = delay0 + Kd1*(vctrl1-vctrl1_0) + Kd2*(vctrl2-vctrl2_0)

where the parameter delay0 is the nominal delay when vctrl1 and vctrl2 are at their nominal values set by the parameters vctrl1_0 and vctrl2_0, respectively. The parameters Kd1 and Kd2 are the control gains of the variable delay element, defined as the rate of change in the delay with respect to the change in vctrl1 and vctrl2, respectively. In addition, the delay may have the maximum and minimum limits, which are set by the parameters delay_max and delay_min, respectively.

This variable delay element model consists of a poly_func, limit, and delay_to_clk primitives, where the poly_func and limit primitives calculate a delay value from the vctrl1 and vctrl2 inputs and the delay_to_clk primitive produces the output clock out by delaying the input clock in with the calculated delay amount.

Input/Output Terminals

| Name | I/O | Type | Description |

| out | output | xbit | output clock |

| in | input | xbit | input clock |

| vctrl1 | input | xreal | control voltage #1 |

| vctrl2 | input | xreal | control voltage #2 |

Parameters

| Name | Type | Default | Description |

| delay0 | real | 0.8n | delay at nominal vctrl value (s) |

| vctrl1_0 | real | 0.5 | nominal value for vctrl1 (V) |

| vctrl2_0 | real | 0.5 | nominal value for vctrl2 (V) |

| Kd1 | real | -3n | delay control gain for vctrl1 (s/V) |

| Kd2 | real | -1.5n | delay control gain for vctrl2 (s/V) |

| delay_max | real | 1.4n | maximum limit on delay (s) |

| delay_min | real | 0.2n | minimum limit on delay (s) |

List of Testbenches

| tb_check : A testbench for checking the basic operation of a variable delay element |

| tb_meas_tfdc : A testbench for measuring the voltage-to-delay (V-to-D) characteristics of a variable delay element |

tb_check : A testbench for checking the basic operation of a variable delay element

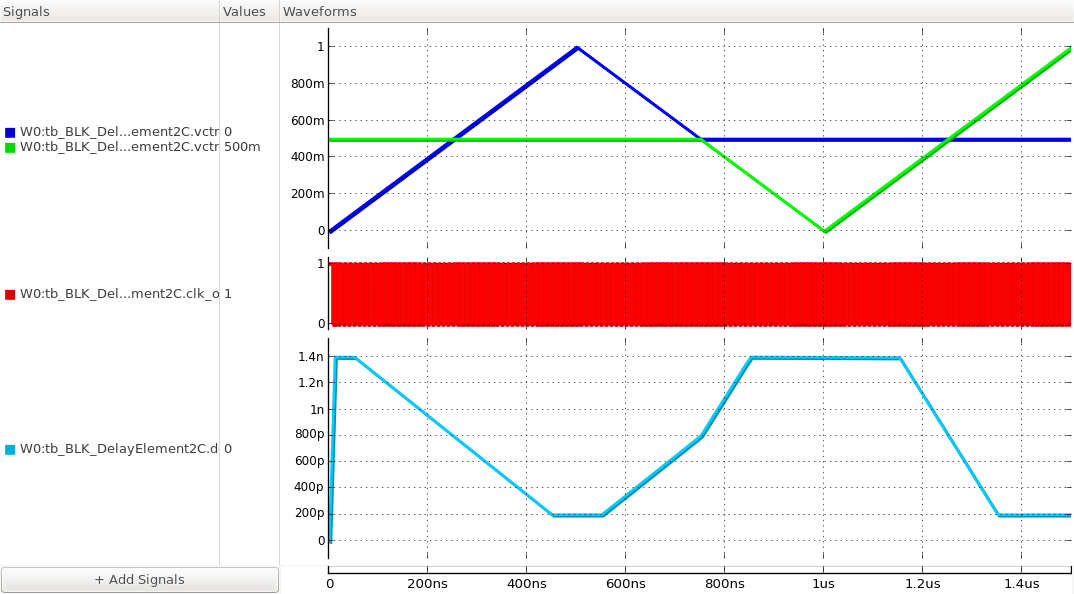

This testbench checks the basic functionality of a variable delay element by feeding a constant-frequency clock and varying its control voltages. The measured input-to-output delay of the variable delay element is expected to change according to its V-to-D characteristics.

Simulation Results

Figure. input and output waveforms.

tb_meas_tfdc : A testbench for measuring the voltage-to-delay (V-to-D) characteristics of a variable delay element

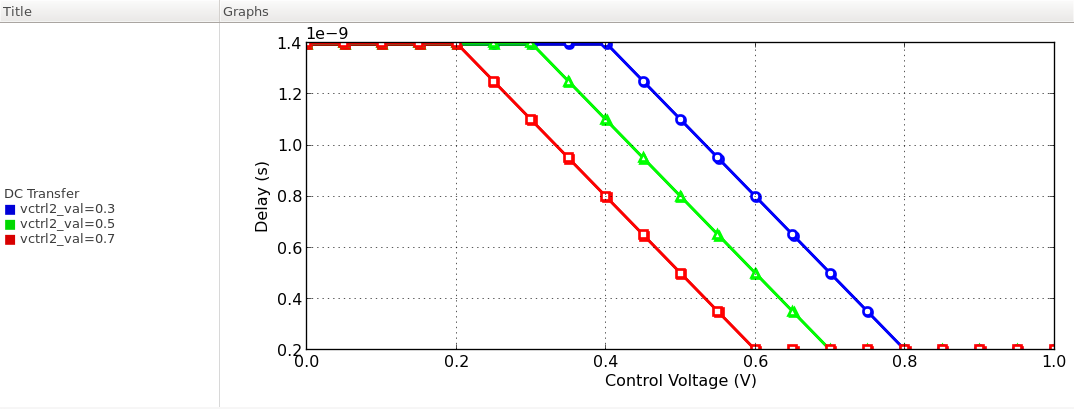

This testbench measures the voltage-to-delay (V-to-D) characteristics of a variable delay element, by gradually varying the control voltage vctrl1 and measuring the delay. The resulting DC transfer characteristics correspond to the V-to-D characteristics of interest.

Simulation Results

Figure. the voltage-to-delay characteristics.