PDC_LinearPFD : A linear phase-frequency detector (PFD)

A linear phase-frequency detector (PFD) compares the timings of two input clocks, clk_ref and clk_fb, and expresses their difference with the pulsewidths of two outputs up and dn. A PFD is capable of measuring both the phase and frequency differences of the two input clocks. When they have close enough frequencies, the PFD outputs indicate their phase difference. On the other hand, when they have large enough frequency difference, the outputs indicate the polarity of the frequency error.

This linear PFD model is composed of two edge-triggered D-filpflops with asynchronous resets and one AND gate. Each D-flipflop asserts its output when the rising edge of its corresponding clock arrives. When the outputs of both the D-flipflops are asserted, the AND gate asserts the signal rst to reset the states of the D-flipflops. The net difference between the up and dn pulsewidths indicates the timing difference between the two input clocks, clk_ref and clk_fb. The parameter delay_rst sets the delay of the AND gate, which determines the period of both the up and dn pulses staying asserted and hence their minimum pulse widths. A finite delay is often required to eliminate a dead-zone in the PFD transfer characteristics.

The model is described using the gate primitives such as dff_rst_async_xbit and and_xbit to process accurate timings of digital pulses without being limited by the simulation timestep.

Input/Output Terminals

| Name | I/O | Type | Description |

| dn | output | xbit | dn output |

| up | output | xbit | up output |

| clk_fb | input | xbit | feedback clock |

| clk_ref | input | xbit | reference clock |

Parameters

| Name | Type | Default | Description |

| delay_rst | real | 10e-12 | reset propagation delay |

List of Testbenches

| tb_meas_tfdc_freq : A testbench for measuring the frequency error vs. net output polarity transfer characteristics of a phase-frequency detector (PFD) |

| tb_meas_tfdc_phase : A testbench for measuring the phase error vs. net output pulsewidth transfer characteristics of a phase-frequency detector (PFD) |

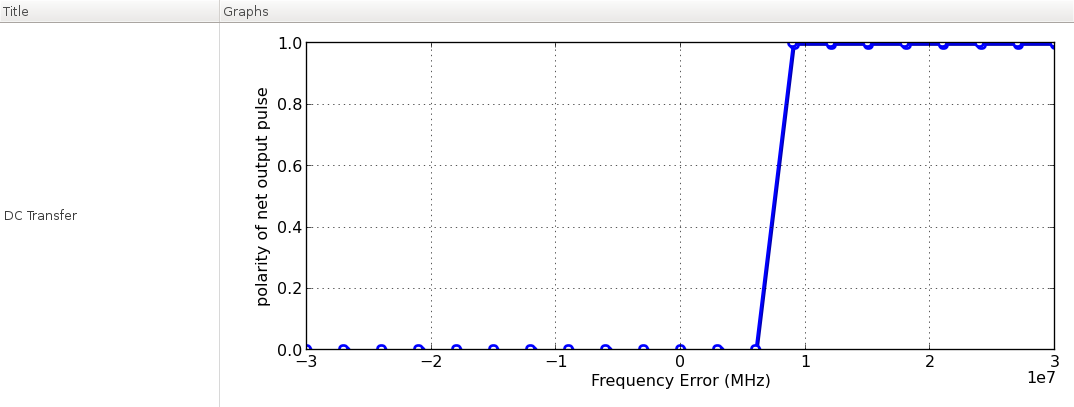

tb_meas_tfdc_freq : A testbench for measuring the frequency error vs. net output polarity transfer characteristics of a phase-frequency detector (PFD)

This testbench measures the frequency error vs. net output polarity transfer characteristics of a phase-frequency detector (PFD). The testbench utilizes a probe_dc primitive to sweep the frequency error between the two input clocks to the PFD and plot the resulting net output polarity.

Simulation Results

Figure. frequency error vs. net output polarity transfer characteristics.

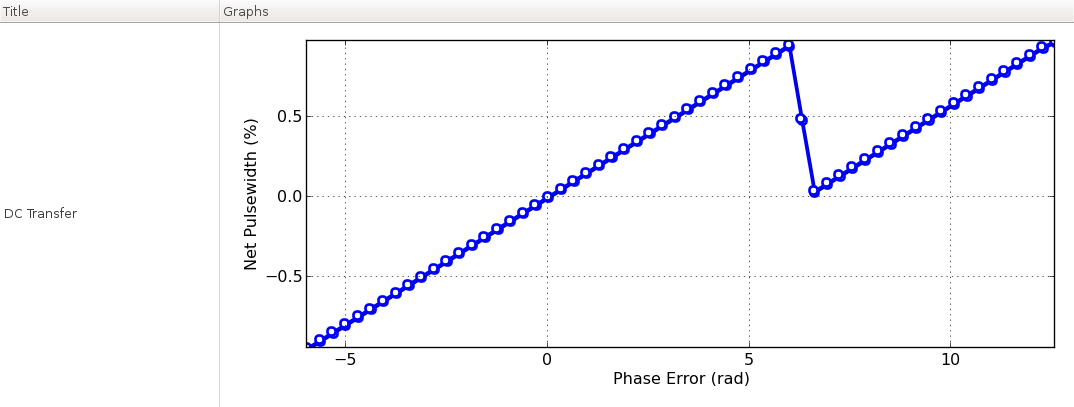

tb_meas_tfdc_phase : A testbench for measuring the phase error vs. net output pulsewidth transfer characteristics of a phase-frequency detector (PFD)

This testbench measures the phase error vs. net output pulsewidth transfer characteristics of a phase-frequency detector (PFD). The testbench utilizes a probe_dc primitive to sweep the phase error between the two input clocks to the PFD and plot the resulting net output pulsewidth as a percentage of the clock period.

Simulation Results

Figure. phase error vs. net output pulsewidth transfer characteristics.