BLK_SRLatch : A set-reset (SR) latch

An SR-latch is a sequential element that sets its output Q when the set input S is 1, resets Q when the reset input R is 1, and holds the current output when both S and R are at 0.

This SR-latch model is described with two cross-coupled nor_xbit primitives. The additional buf_xbit primitives are to enforce an initial output value, set by the parameter init_value. The model also provides an complementary output Qb. The outputs of the SR-latch is ill-defined when both the S and R inputs are 1 and this model may exhibit an oscillation in that case.

The model is composed of the XMODEL gate primitives to process the precise timing information of the input signals without being limited by the simulation timestep of SystemVerilog.

Input/Output Terminals

| Name | I/O | Type | Description |

| Q | output | xbit | output (pos) |

| Qb | output | xbit | out (neg) |

| R | input | xbit | reset input |

| S | input | xbit | set input |

Parameters

| Name | Type | Default | Description |

| init_value | bit | 1’bx | initial output value |

List of Testbenches

| tb_check : A testbench for checking the basic operation of a set-reset (SR) latch |

tb_check : A testbench for checking the basic operation of a set-reset (SR) latch

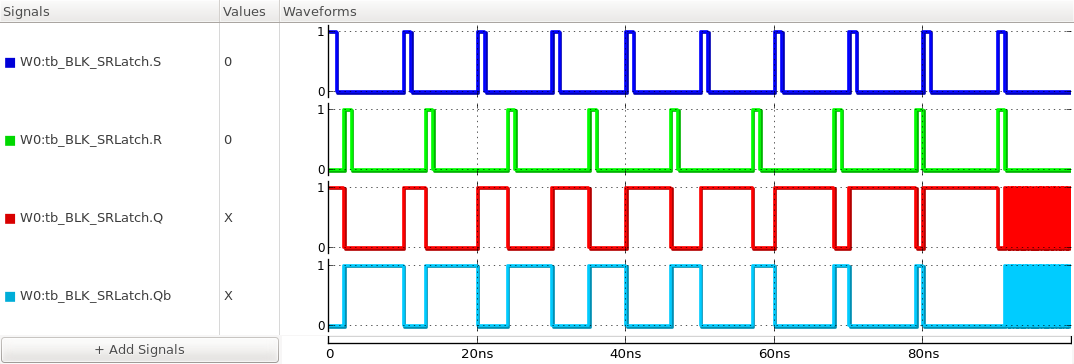

This testbench checks the basic functionality of an SR-latch by supplying a sequence of pulses to its set (S) and reset (R) inputs and observing the outputs Q and Qb. The Q output is expected to switch to 1 when S rises and switch to 0 when R rises. The Qb output should take the complementary value of the Q output. The behavior of the SR-latch is ill-defined when both the S and R inputs are high and this model may exhibit an oscillation in that case.

Simulation Results

Figure. input and output waveforms.