Overview

MODELZEN is an automatic model generator for analog circuits that can translate any circuit netlist into an equivalent XMODEL circuit-level model. The generated model can be simulated entirely in a SystemVerilog simulator employing the XMODEL simulation engine. It is most suitable for generation of bottom-up models for analog circuits with which one can perform efficient verification of large, complex analog/mixed-signal systems in SystemVerilog.

MODELZEN is different from MODELFIT in that it is a structural modeling tool rather than a functional modeling tool. In other words, rather than modeling the functionality of the circuit under consideration, MODELZEN preserves the structure of the circuit (i.e. the topology) while mapping each of its individual devices into an equivalent XMODEL circuit-level primitive. This approach is possible mainly because XMODEL can perform circuit-level simulation in SystemVerilog; a feature not supported by Real-Number Modeling.

The main advantage of MODELZEN is that one can generate high- fidelity analog models directly from circuit netlists without requiring any knowledge or expertise on the circuits. For instance, a verification engineer can generate models from the circuit database for system-level verification without asking for a help from the circuit designer. Also, one can setup an automation flow that re-generates new models every time the circuits are updated in order to keep the consistency between the models and circuits. MODELZEN is also convenient when a circuit has many digital mode switches of which manual modeling can be quite labor-intensive and error-prone.

This document explains the basic concepts and usages of MODELZEN.

MODELZEN Basics

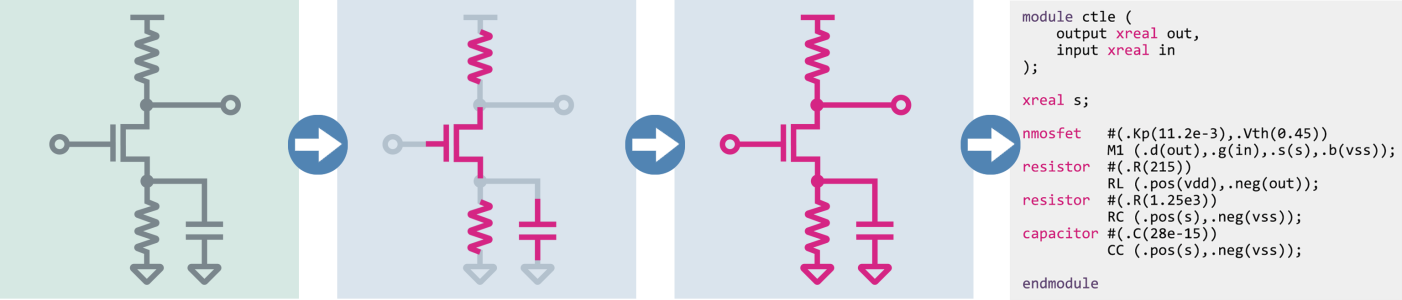

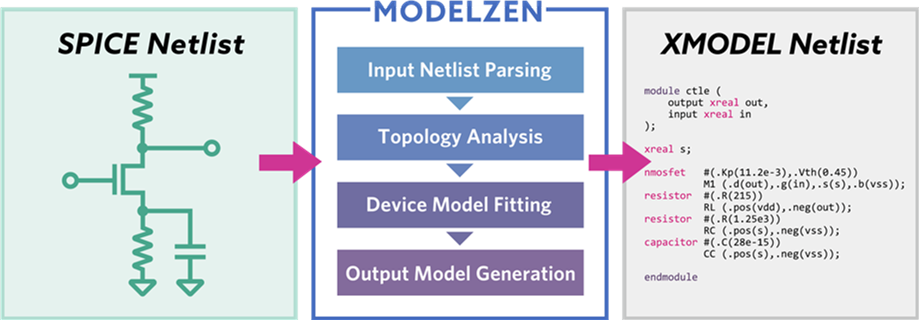

Figure 1 illustrates the overall process of generating models in MODELZEN and Figure 2 illustrates the key steps in doing so.

Figure 1. Process of generating models in MODELZEN.

- First, the input circuit netlist described in either SPICE, CDL, or Spectre format is parsed and converted to a network of circuit elements.

- Second, the topology of the circuit is analyzed and processed to reduce its complexity. For instance, parallel or series devices are merged and too large shunt resistors or too small series resistors are trimmed.

- Third, each unique device element composing the processed circuit network is characterized via SPICE simulation and curve- fitted to the corresponding XMODEL circuit primitive model.

- Finally, a SystemVerilog model is generated by listing the resulting XMODEL primitive models with the same connections with the processed network.

Figure 2. Key processing steps in MODELZEN.

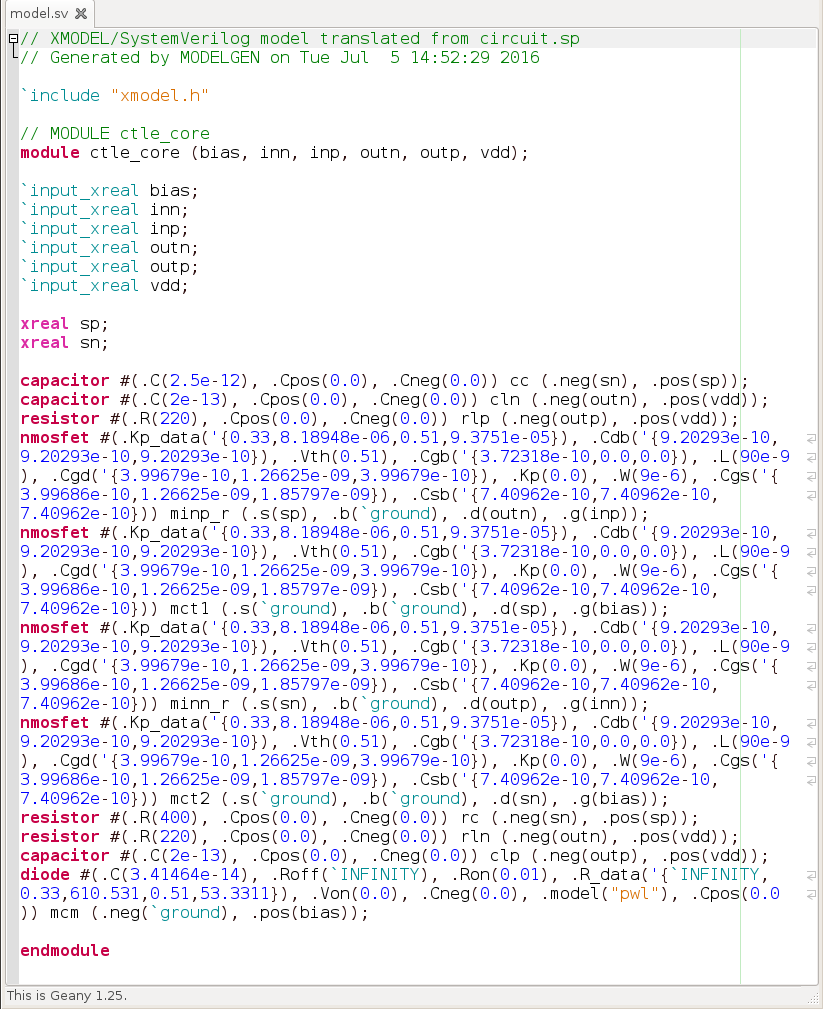

Note that the model generated by MODELZEN consists of XMODEL circuit-level primitives and hence can be simulated only in XMODEL. In fact, this kind of structural model generation is only possible in simulators that support circuit-level modeling. For more details on circuit-level modeling (CLM) in XMODEL, please refer to the XMODEL User Guide.

Figure 3. An example circuit-level model generated by MODELZEN.

MODELZEN Key Features

The key features of MODELZEN are as listed:

- MODELZEN can be run both in graphical-user interface (GUI) and command-line modes and also from Cadence® Virtuoso® Schematic Editor.

- MODELZEN can process circuit netlists either in HSPICE, CDL, or Spectre format.

- For device-level characterization, MODELZEN uses commercial SPICE simulators such as HSPICE, Spectre, or FineSim and hence can generate models from circuits described using any SPICE models supported by these simulators.

- MODELZEN supports multi-threading while running SPICE simulation for device-level characterization. In other words, MODELZEN can launch multiple SPICE simulations that run in parallel to speed up the model generation process.

- MODELZEN can recycle the previously-run SPICE characterization results and save time running redundant simulations.

- MODELZEN offers various tailoring options at the cell- and instance-levels to fine-tune the generated model’s accuracy and speed.

- MODELZEN can also translate .MEASURE and .IC statements embedded in the circuit netlist into equivalent XMODEL primitives.