- Languages:

- English

- Korean

신호가 원하는 범위내에서 일정한 시간동안 유지되었는지를 체크하는 방법

LDO 레귤레이터 회로를 위한 assertion check들을 작성하고 있습니다. 출력 전압 'Vout'이 지정된 범위 내에서 일정 시간 동안 유지되었는지를 판단하고, 그 결과를 사용해 다른 assertion check들을 활성화하고 싶습니다. 예제를 통해 이 방법을 알려주실 수 있을까요?

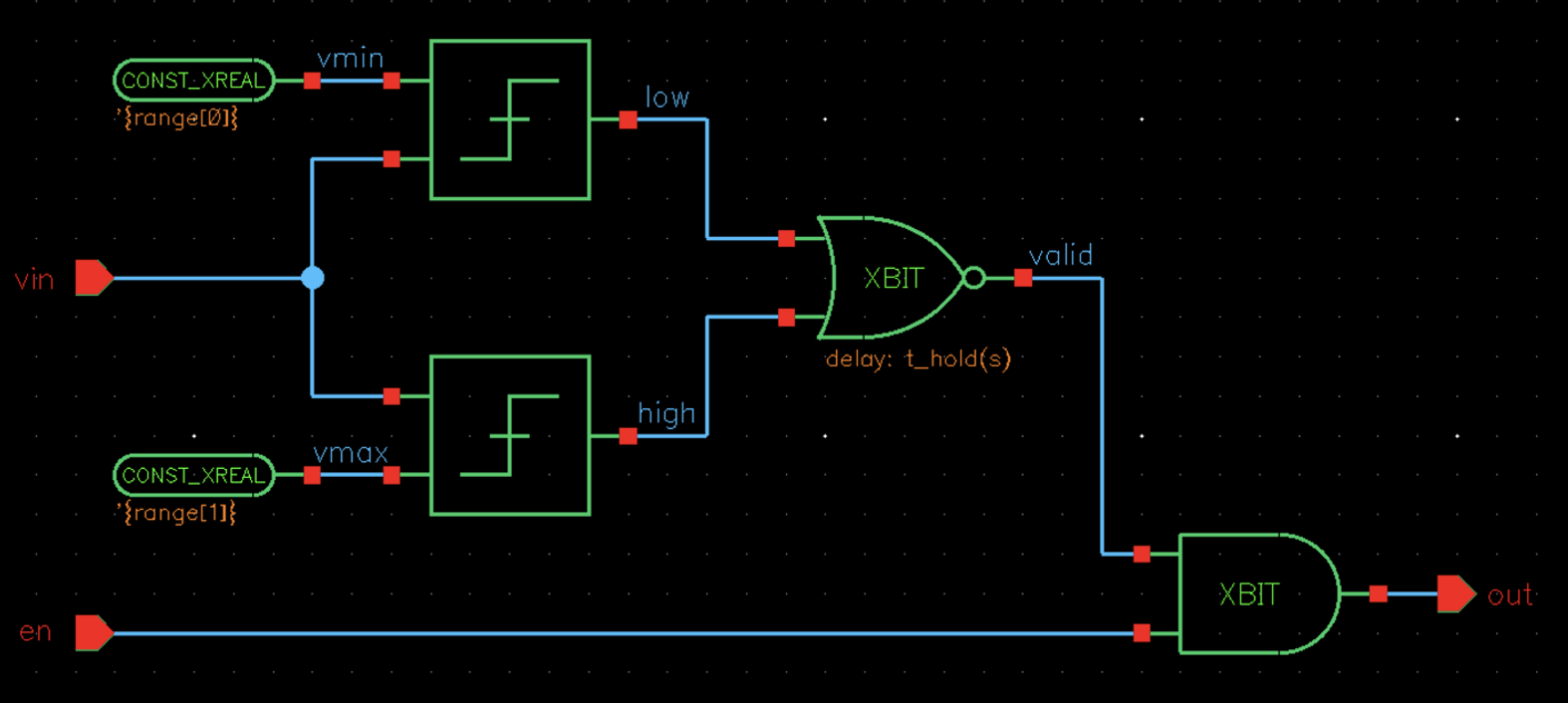

물론이죠. 첨부된 패키지에 포함된 아래의 sandbox.chk_settle:schematic cellview는 어떤 아날로그 신호가 일정 시간 동안 지정된 범위 내에서 유지되었는지를 판별하는 예를 보여줍니다. 참고로, 이 범위의 최소값과 최대값은 실수형 배열 파라미터 'range[0:1]' 로 정의되며, 신호가 해당 범위 내에 머물러야 하는 최소 시간은 파라미터 't_hold'로 정의하고 있습니다.

먼저, 두개의 'slice' primitive들이 입력 신호 'vin' 을 지정된 범위의 최소값 및 최대값과 비교하여, 신호가 너무 낮은지('low') 또는 너무 높은지('high')를 각각 판별합니다. 이후 'nor_xbit' primitive가 이 두 결과를 조합하여 'vin'이 지정된 범위 내에 있는지를 나타내는 'valid' 신호를 생성합니다. 이 'nor_xbit' primitive는 't_hold' 만큼의 지연시간을 가지는데, 그 관성 지연(inertial delay) 특성으로 인해 'low'와 'high' 신호가 모두 0인 상태를 't_hold' 동안 유지할 때에만 'valid' 가 1로 변합니다. 마지막으로, 출력 신호는 'en' 입력과 AND 연산되어, 'en' 이 0으로 바뀌는 즉시 최종 출력도 0으로 바뀌도록 합니다.

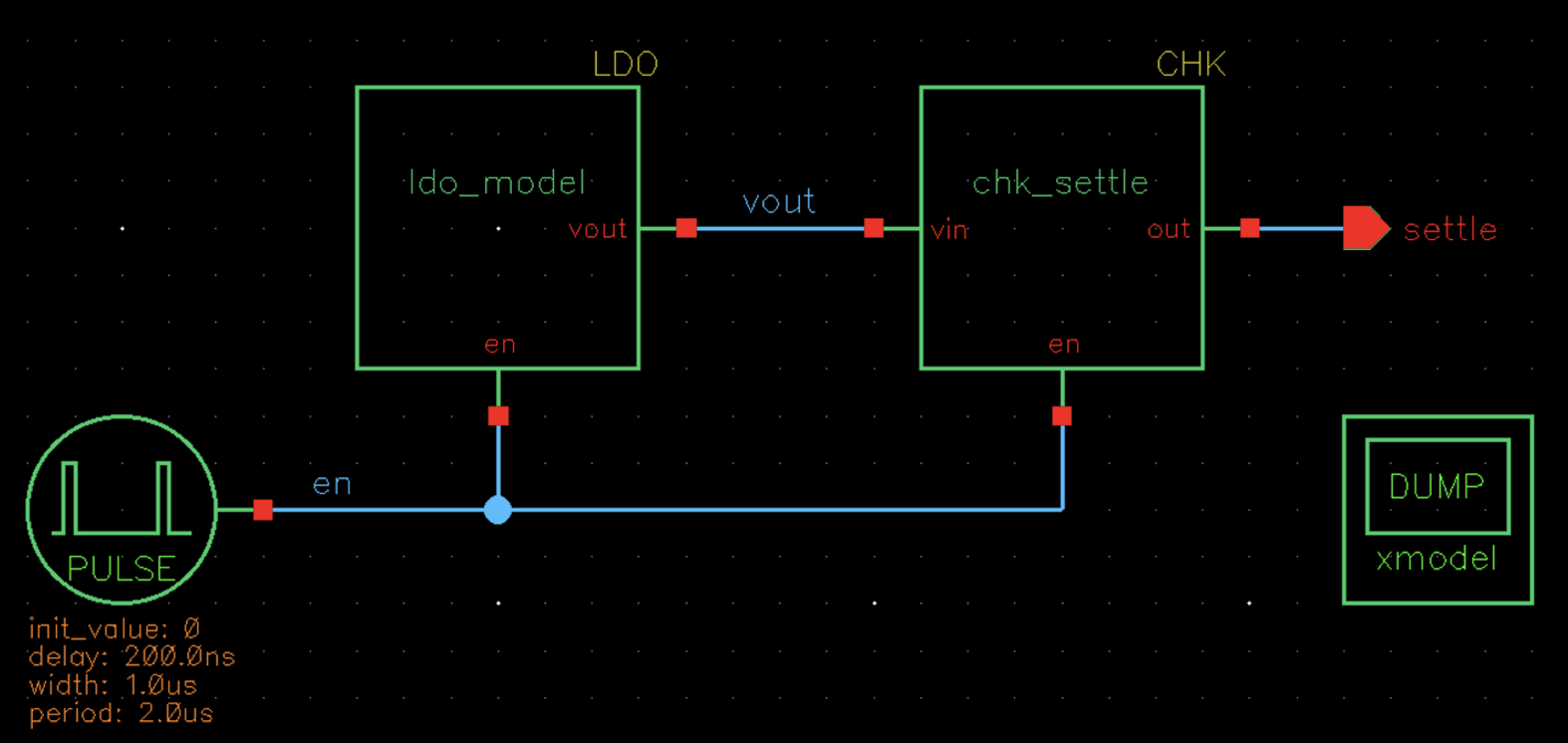

아래의 sandbox.tb_chk_settle:schematic cellview는 이 checker의 동작을 확인하기 위한 테스트벤치입니다. 'en' 신호는 주기적으로 0과 1 사이를 스위칭하며, LDO를 표현하는 모델은 'en' = 1 일 때 0.8V, 'en' = 0 일 때 0.0 V의 출력을 생성하고, 그 스위칭 과정에서의 transient 현상도 함께 표현합니다. 앞서 설명한 'chk_settle' 셀은 이 LDO 모델의 출력 전압 'vout' 을 모니터링하며, 'vout'이 0.79V 와 0.81V 사이에서 50ns 동안 유지될때 'settle' 신호를 1로 만듭니다.

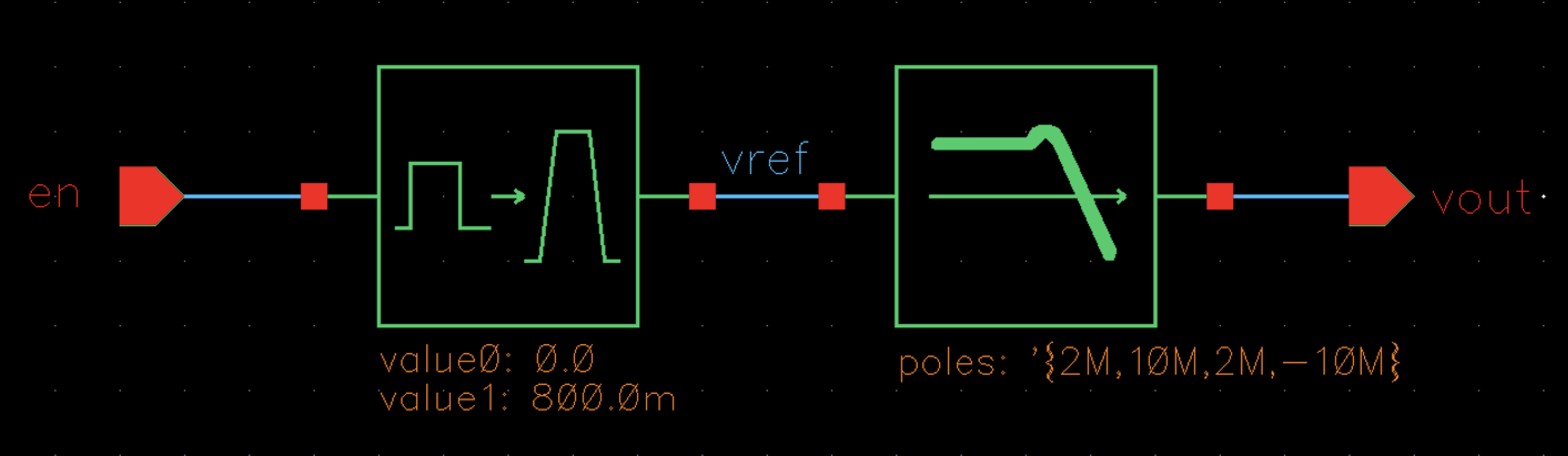

참고로, 아래의 sandbox.ldo_model:schematic cellview는 LDO 레귤레이터가 활성화되거나 비활성화될 때의 과도(transient) 동작을 에뮬레이션합니다. 'transition' primitive는 'en' = 1 일 때 출력 전압의 최종 값을 0.8 V, 'en' = 0 일 때는 0.0 V 로 설정합니다. 또한 'filter' 프리미티브는 2차 low-pass 시스템의 underdamped 응답 형태로 과도 동작을 모델링합니다.

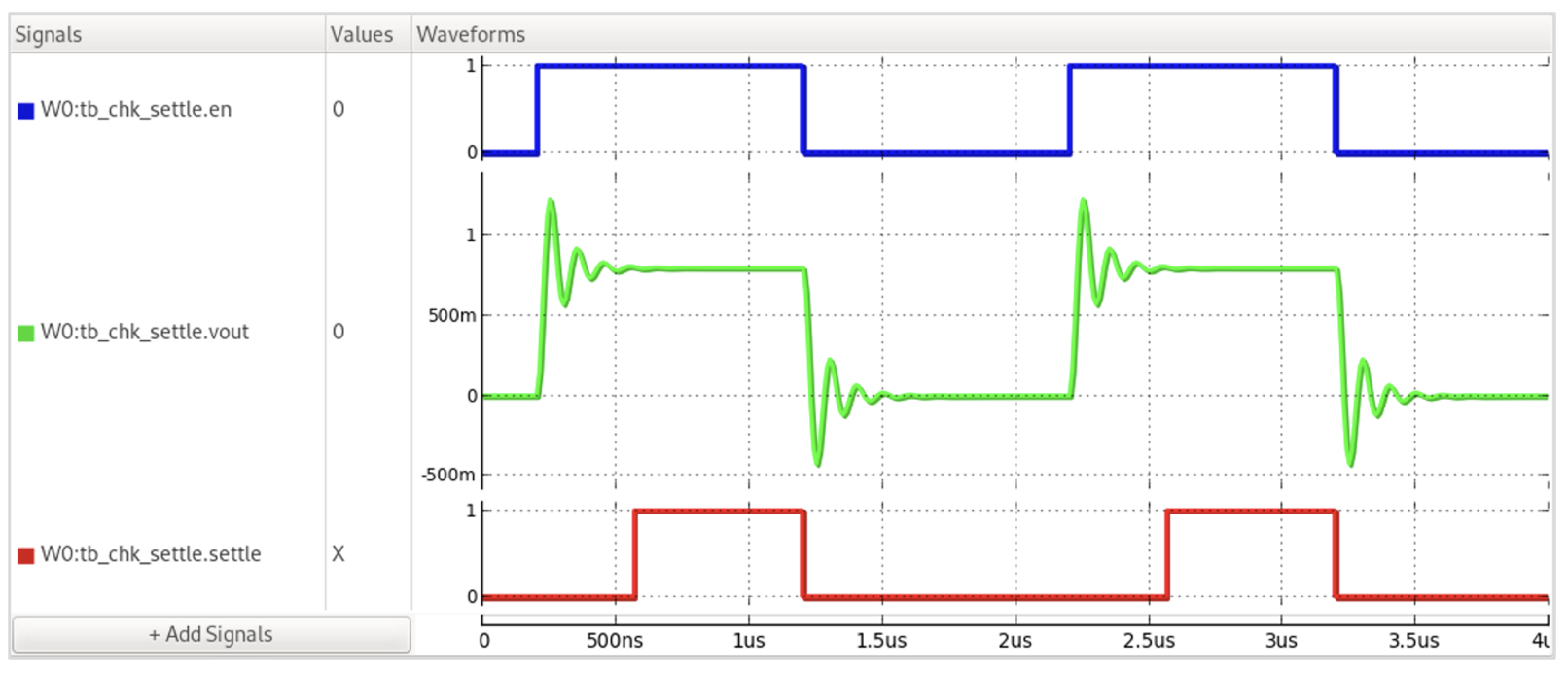

아래는 이 'tb_chk_settle' testbench를 사용해 시뮬레이션한 파형들입니다. LDO 모델의 출력 전압 'vout'이 [0.79, 0.81] 의 지정된 범위 내에서 50ns 동안 유지되면 'settle' 신호가 1로 바뀌며, 'en' 신호가 0이 되면 그 즉시 다시 0으로 바뀝니다.

Please login or Register to submit your answer