- Languages:

- English

- Korean

GLISTER를 사용해 Real-Number Model (RNM) 타입의 포트를 가진 모델 스키매틱을 netlisting할 수 있나요?

GLISTER를 사용해 탑다운 모델링을 하고 있습니다. 제 모델 스키매틱들 중 일부는 real-number model (RNM)과 연결되어야 하는데, 그 연결되는 포트는 wreal1driver, wreal4state, wrealsum, wrealavg, wrealmax, 또는 wrealmin와 같은 RNM nettype을 갖고 있습니다. 제 모델 스키메틱의 몇몇 포트의 신호 타입을 이러한 RNM nettype으로 정의하고, 그 스키메틱으로부터 적절한 타입 커넥터를 자동 삽입한 SystemVerilog netlist를 생성할 수 있나요?

예, 물론입니다. 먼저 GLISTER 환경에서 real-number model (RNM) nettype들을 사용하려면, 아래의 내용을 Cadence의 .cdsinit 초기화 파일 내에 추가해주어야 합니다.

;------------------------------------------------------------

; GLISTER support for real-number model (RNM) nettypes

;------------------------------------------------------------

xmodelSetSigTypeCompatReal(

"wreal1driver"

"wreal4state"

"wrealsum"

"wrealavg"

"wrealmax"

"wrealmin"

)

여기서 쓰인 xmodelSetSigTypeCompatReal( <type1> <type2> … )는 GLISTER 환경에서 사용할 real과 호환되는 nettype의 리스트를 정의하는 GLISTER API 함수입니다. 비슷한 형식의 xmodelAddSigTypeCompatReal( <type1> <type2> … ) 함수는 기존의 리스트에 새로운 nettype을 추가하고자 할때 사용할 수 있습니다.

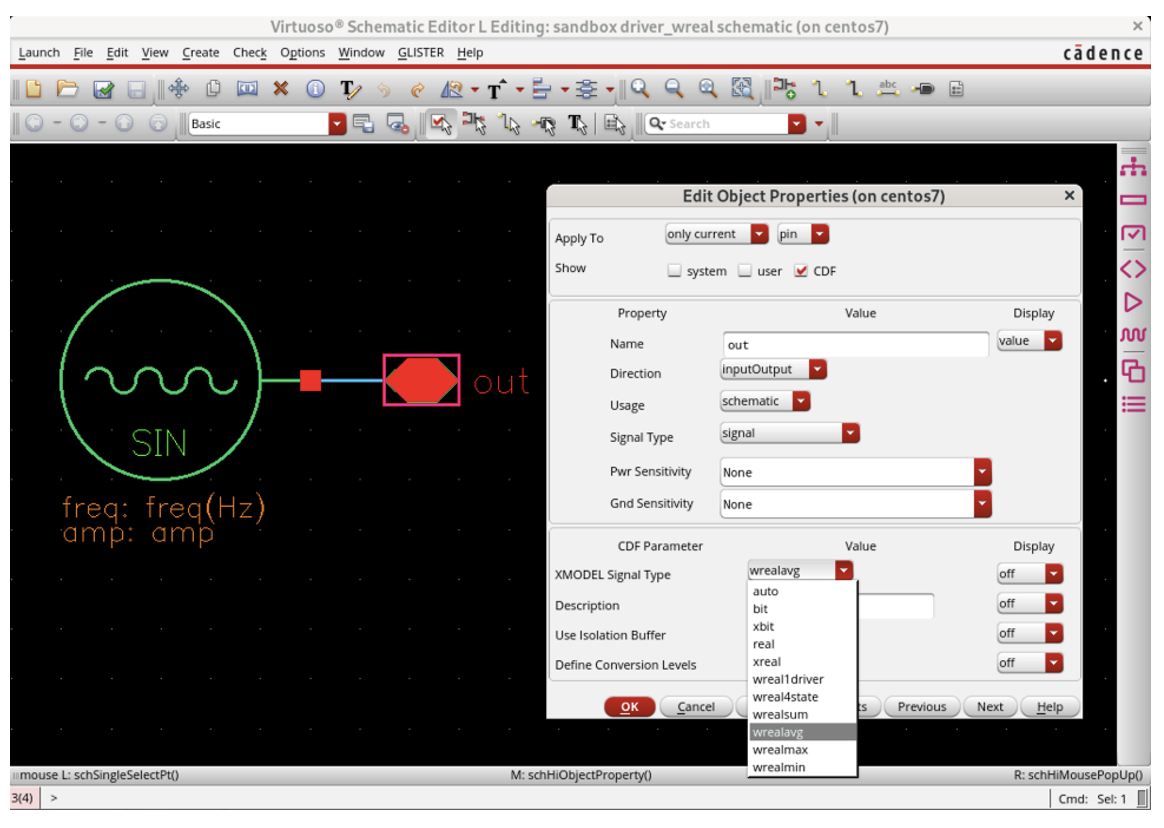

예를 들어, 첨부한 패키지에는 sandbox.driver_wreal:schematic라는 이름의 cellview가 들어 있는데, 이는 단순히 하나의 sin_gen primitive가 'out'라는 이름의 inputOutput 포트를 통해 정현파를 구동하도록 구성되어 있습니다. 이 포트에 대한 Edit Object Properties 창을 열어보면, XMODEL Signal Type 필드에 이전보다 선택지가 많아졌음을 보실겁니다. 즉, xmodelSetSigTypeCompatReal() 함수로 정의한 RNM nettype들이 추가로 선택가능해졌습니다. 이 예제에서는 'wrealavg' 타입을 선택해서, 복수의 이 셀이 공통의 wrealavg 타입 net을 구동할때, 그 net 신호의 값이 각 driver 셀이 출력하는 신호들의 평균값이 되도록 하였습니다. 복수의 드라이버가 하나의 net을 구동해야 하기 때문에 그 포트도 양방향의 inputOutput 포트로 정의하였습니다.

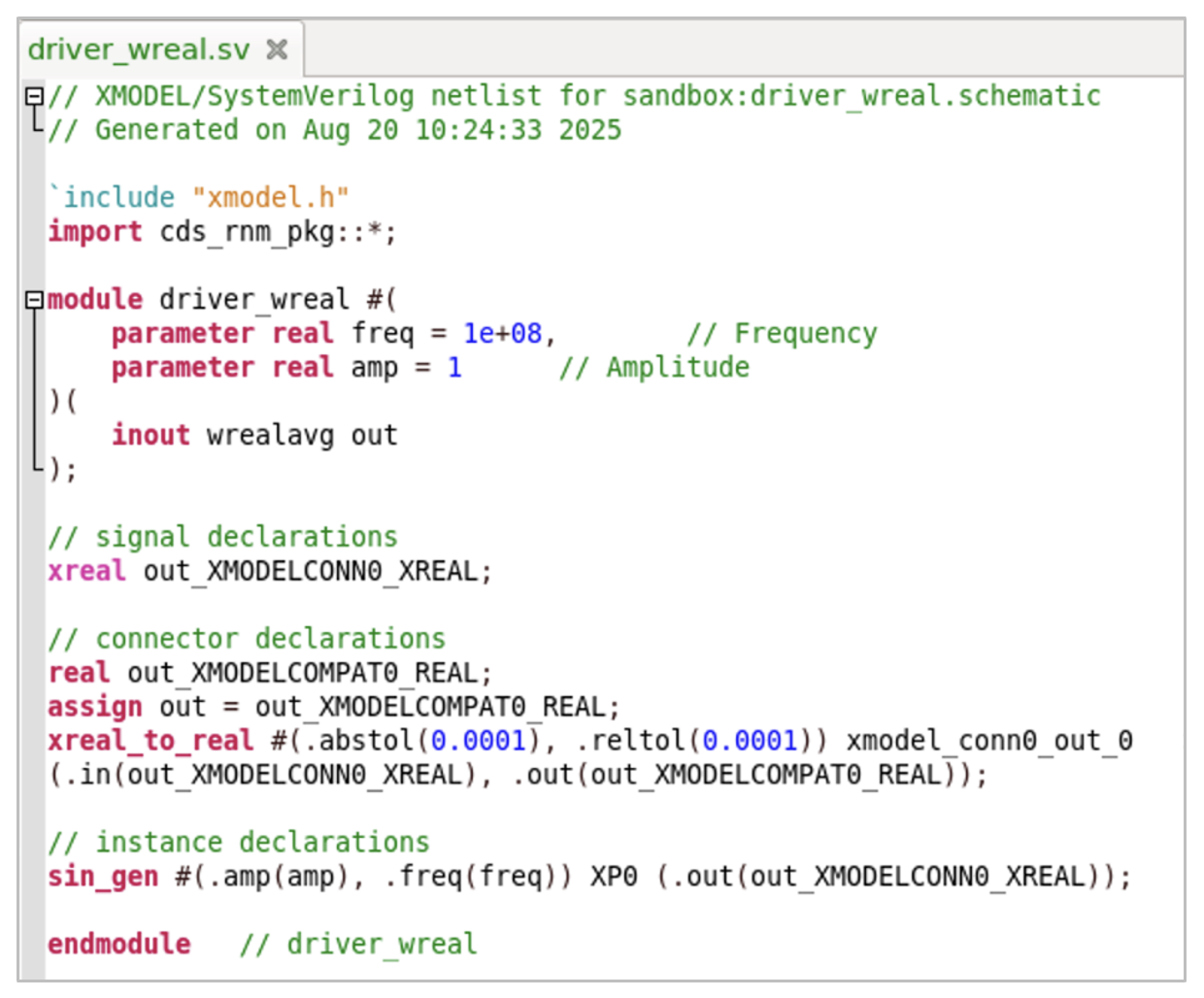

아래는 GLISTER가 이 스키매틱으로부터 추출한 SystemVerilog 파일입니다. 의도한대로 포트 'out'가 'wrealavg' 타입의 양방향 inout 포트로 정의되어 있음을 확인할 수 있습니다. 또한, GLISTER가 sin_gen primitive의 xreal 타입 출력을 real 타입 신호로 변환해주는 xreal_to_real primitive와, 이 real 타입 신호를 wrealavg 타입의 inout 포트인 'out'으로 인가해주는 assign 구문을 자동으로 삽입해주었음을 확인할 수 있습니다.

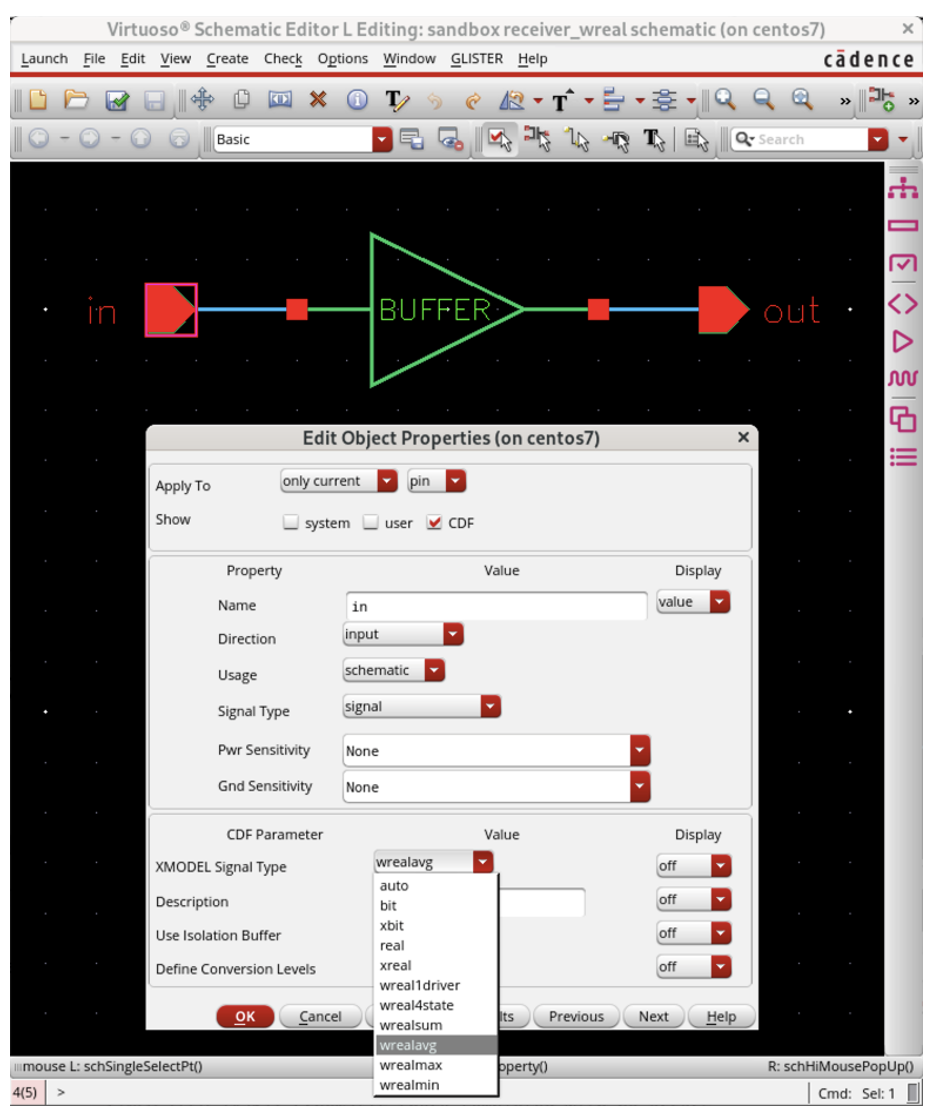

또다른 cellview인 sandbox.receiver_wreal:schematic은 RNM nettype의 입력 포트 또한 정의할 수 있음을 보여줍니다. 이 cell은 기본적으로 wrealavg 타입의 입력을 xreal 타입의 출력으로 전달해주는 buffer primitive로 구성되어 있습니다. 이때, 그 입력 포트의 XMODEL Signal Type 또한 그 포트의 Edit Object Properties 창을 통해 'wrealavg'으로 설정할 수 있습니다.

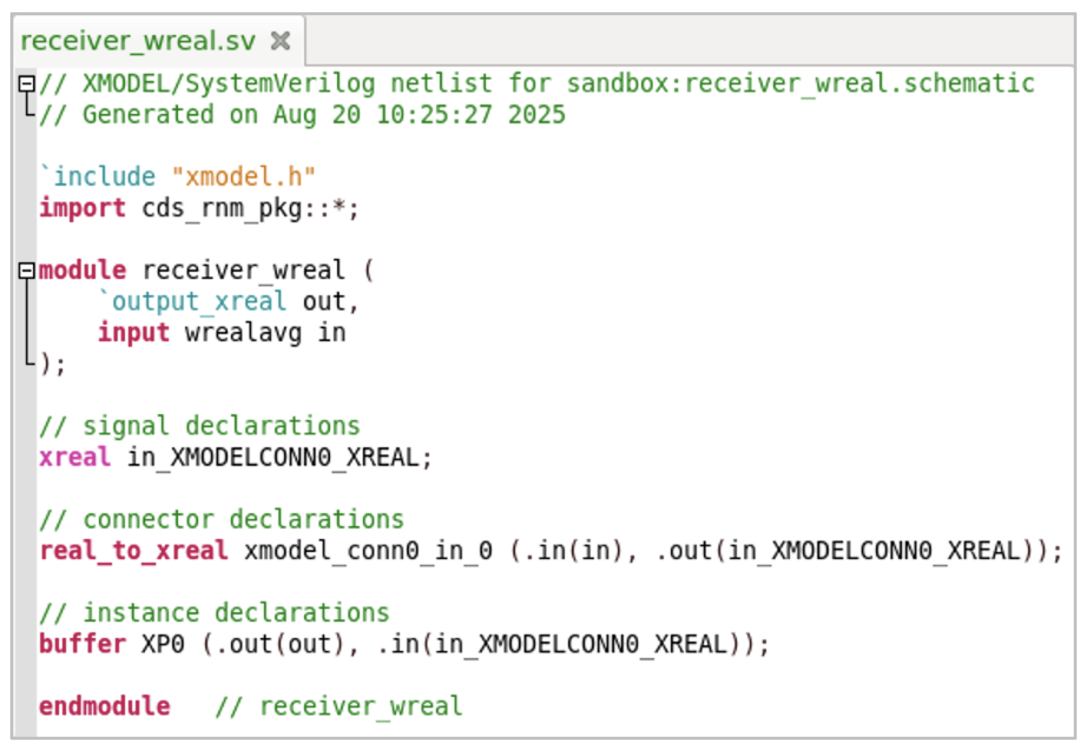

이 스키매틱으로부터 추출한 SystemVerilog 파일도 아래에 보입니다. 입력 포트 'in'이 'wrealavg' 타입으로 선언되어 있고, 이 wrealavg 타입 입력을 buffer primitive의 입력을 구동하기 위한 xreal 타입 신호로 변환해주는 real_to_xreal primitive 또한 삽입되어 있음을 확인할 수 있습니다. 그러면 buffer primitive는 이 신호를 받아 xreal 타입의 출력인 'out'으로 전달하게 됩니다.

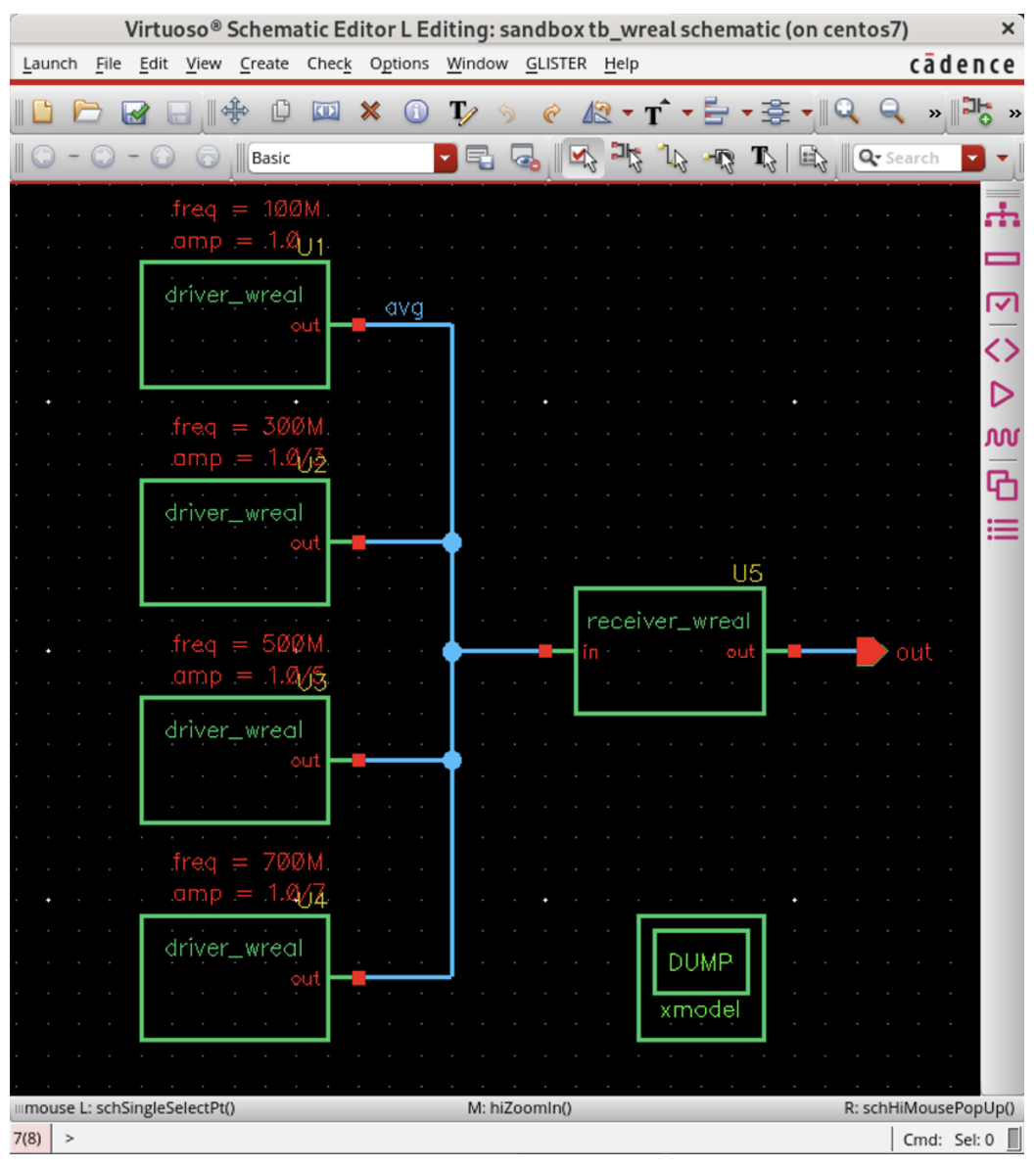

아래의 cellview sandbox.tb_wreal:schematic는 앞서 설명한 driver_wreal와 receiver_wreal를 조합해 구성한 테스트벤치입니다. 4개의 driver_wreal 셀들은 각각 100, 300, 500, 700MHz의 주파수와 1.0, 1.0/3, 1.0/5, 1.0/7의 진폭을 갖는 정현파 신호를 구동합니다. 이들은 100MHz 구형파 신호의 퓨리에 성분들이기 때문에, 4개의 정현파 신호를 하나로 묶어 이들의 평균값을 취하게 되는 wrealavg 타입의 신호 'avg'와 xreal 타입의 최종출력 신호 'out'는 구형파에 가까운 파형을 가질 것임을 예상할 수 있습니다.

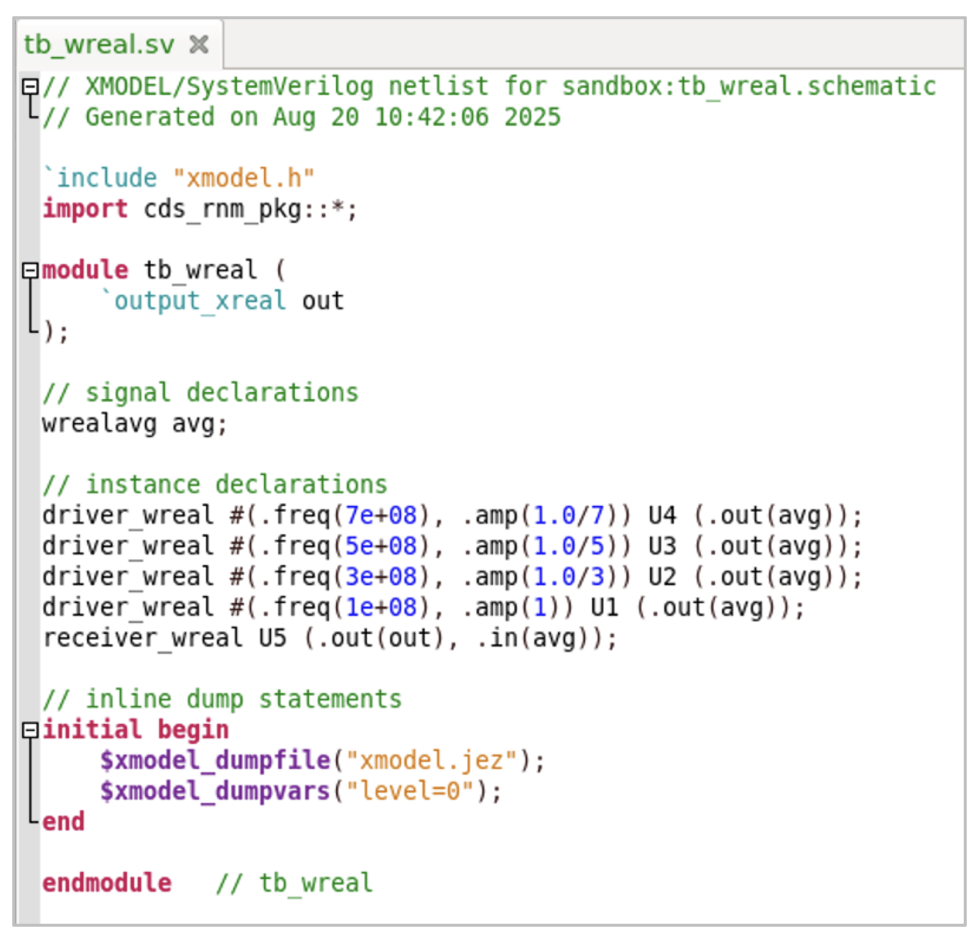

아래는 이 스키매틱으로부터 추출한 SystemVerilog 파일입니다. 신호 'avg'가 'wrealavg' 타입으로 정의되어 있고, 이 신호가 4개의 driver_wreal 셀들의 출력과 receiver_wreal 셀의 입력을 서로 연결합니다.

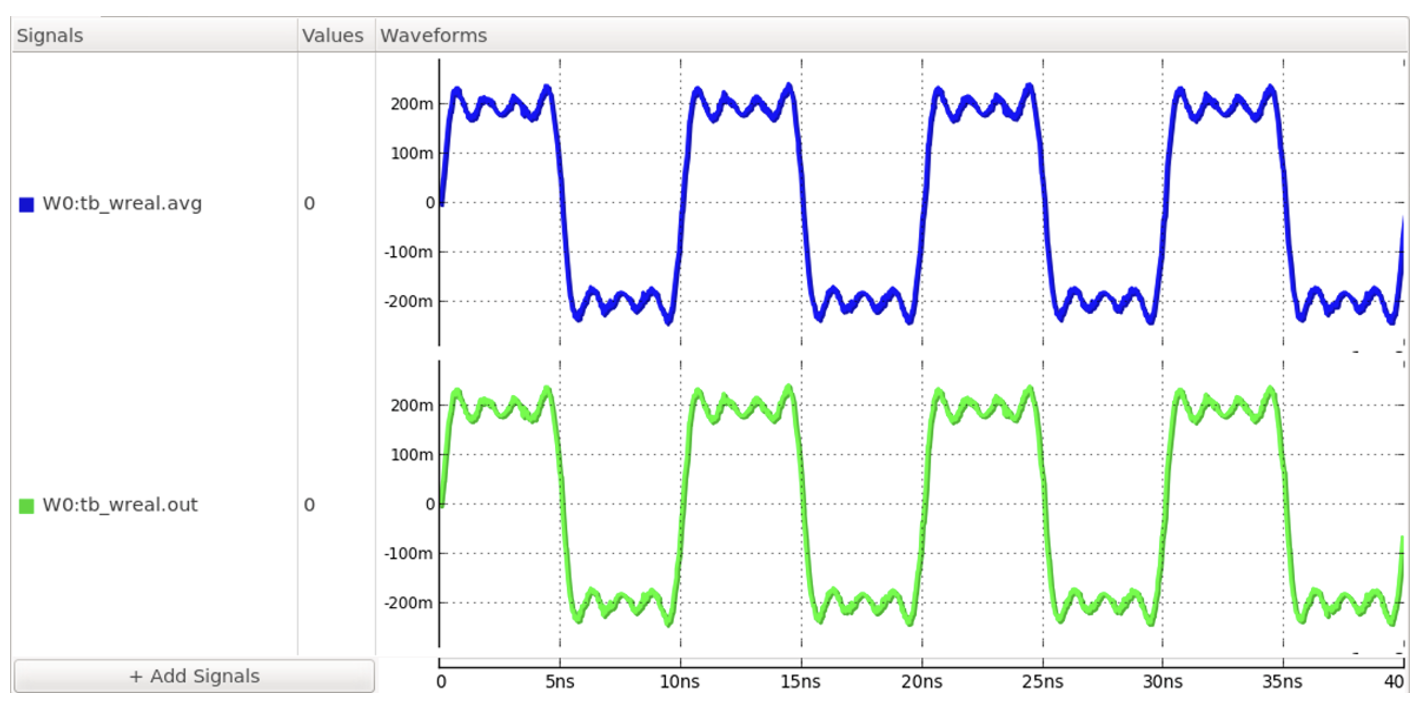

다음은 'avg'와 'out' 신호의 시뮬레이션된 파형입니다. 예상한대로, 그 파형이 100MHz의 구형파에 가까움을 확인할 수 있습니다.

앞에서 보여드린 SystemVerilog 파일들에는 모두 import 구문이 서두에 들어있었음을 보셨나요? (import cds_rnm_pkg::*;) 문제는 VCS, Xcelium, 그리고 Questa 시뮬레이터들이 모두 RNM nettype들을 다른 이름의 패키지 안에서 정의하고 있어서, 이 import 구문이 시뮬레이터에 따라 달라져야 한다는 점입니다. 시뮬레이터에 따라 달라지는 import 구문을 SystemVerilog 파일의 서두에 삽입하는 것은 아래의 라인들을 .cdsinit 초기화 파일에 추가하면 됩니다. 이에 대한 보다 자세한 내용은 또다른 Q&A 포스팅을 참고해주시기 바랍니다.

xmodelModuleFileHeader->vcs = strcat(

"`include \"xmodel.h\"\n"

"import snps_msv_nettype_pkg::*;\n"

)

xmodelModuleFileHeader->xcelium = strcat(

"`include \"xmodel.h\"\n"

"import cds_rnm_pkg::*;\n"

)

xmodelModuleFileHeader->questa = strcat(

"`include \"xmodel.h\"\n"

"import mgc_rnm_pkg::*;\n"

)

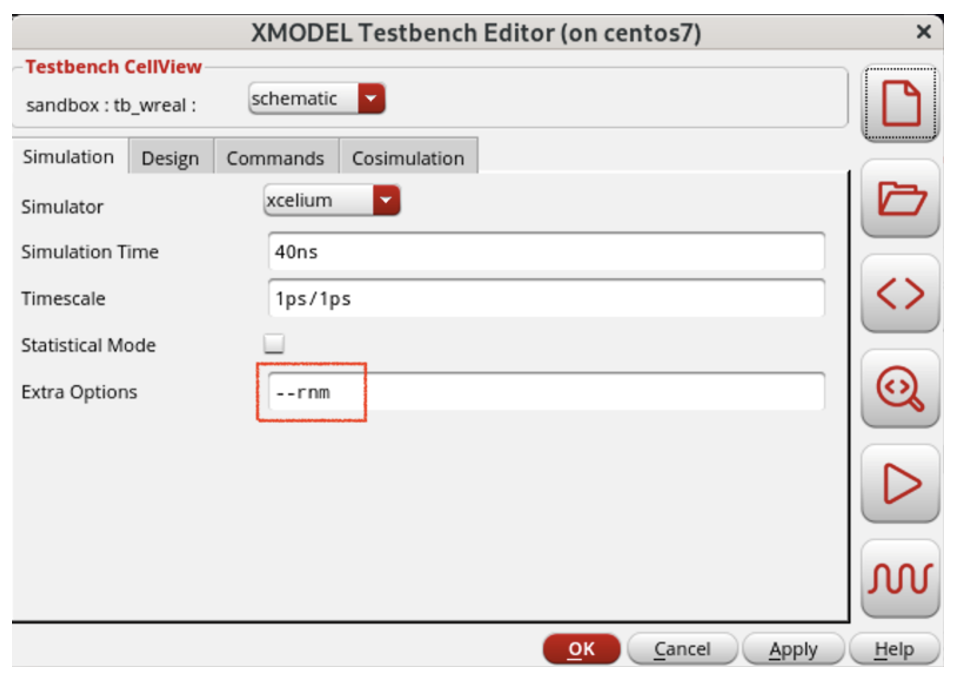

또다른 방법으로는, XMODEL 시뮬레이션을 수행할때 아래에 보이는 것처럼 '--rnm' 옵션을 주는 방법이 있습니다. 이 옵션을 사용하면, 각 시뮬레이터에 특화된 RNM 패키지의 import가 xmodel.h 헤더 파일 내에서 활성화됩니다.

시뮬레이션된 wrealavg 타입의 신호 'avg'를 자세히 살펴보면, 그 신호가 많은 수의 event를 생성하고 있으나, 그에 비해 정확도는 그리 높지 않음을 알 수 있습니다. 사실 보여드린 파형을 얻기 위해서는, 아래의 라인들을 .cdsinit 파일 내에 포함시켜서 오차 범위를 좁혀야 했습니다.

;------------------------------------------------------------ ; defining tolerance for xreal_to_real connectors ;------------------------------------------------------------ xmodelConvXrealToRealAbsTol = 1e-4 xmodelConvXrealToRealRelTol = 1e-4

하지만 여전히 정확도는 충분히 높아지지 않는데, 복수의 wrealavg 신호들이 서로 short될때 그 평균값을 계산하는 resolution function이 유한한 오차를 갖기 때문으로 생각됩니다.

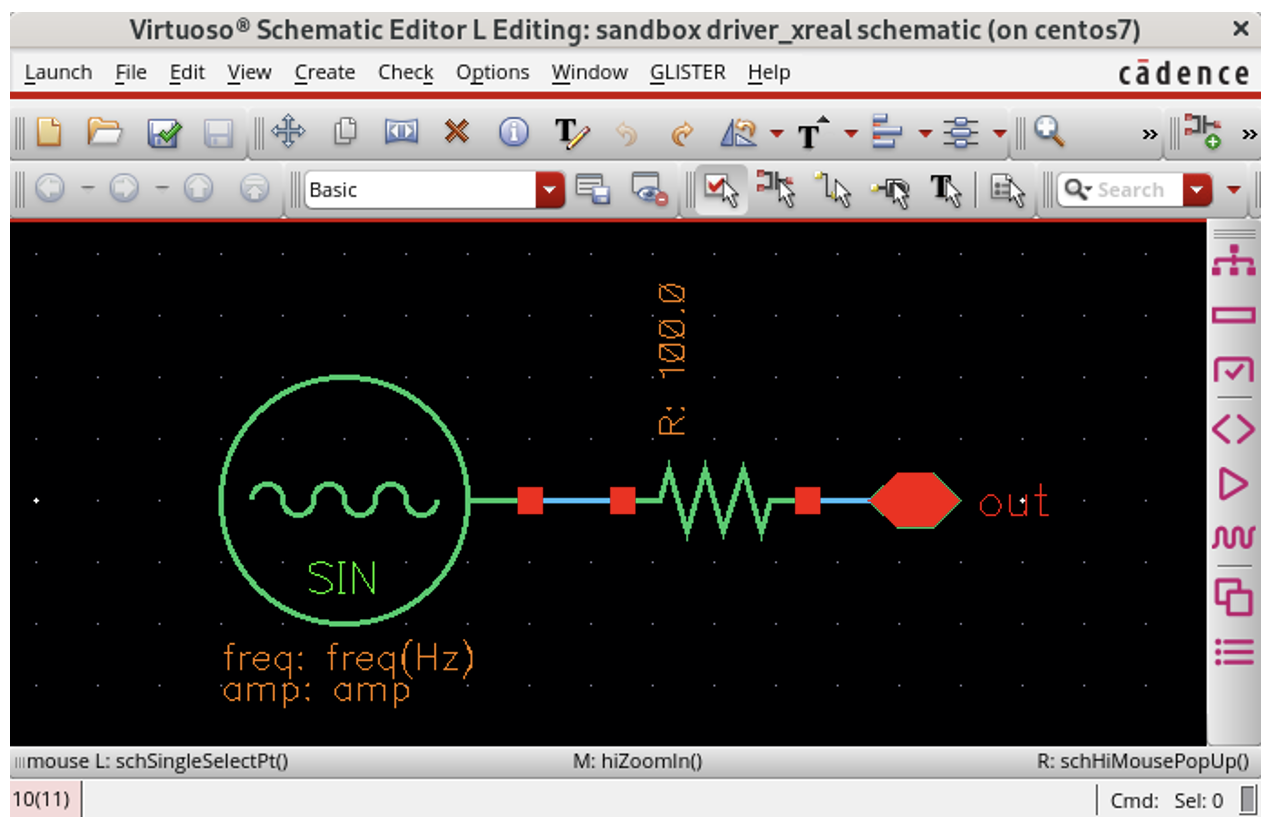

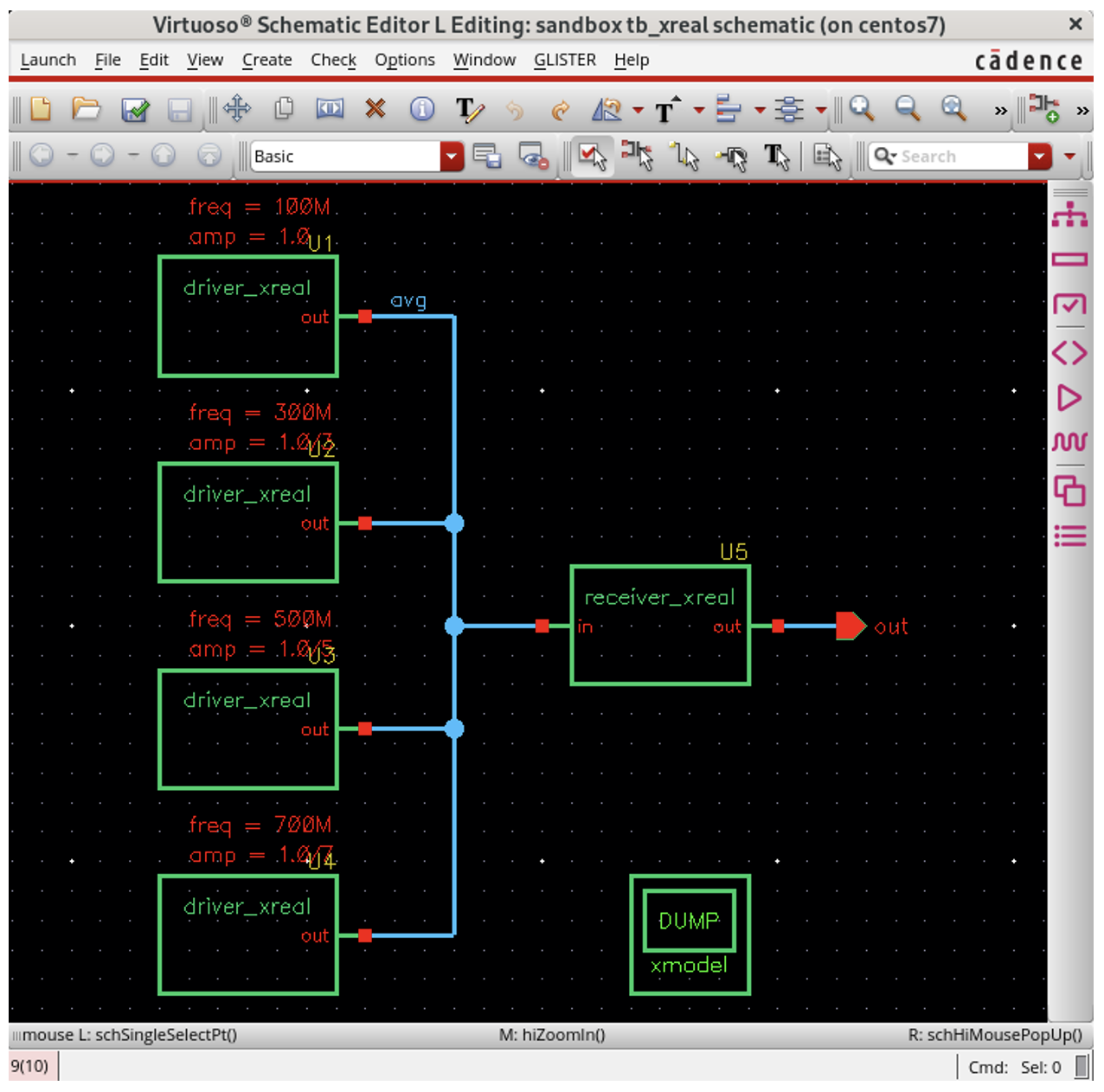

한편, 패키지에 함께 들어있는 cellview인 sandbox.tb_xreal:schematic는 복수의 드라이버 셀 출력들의 평균값을 구하는 XMODEL의 방식을 보여줍니다. 각 드라이버 셀인 sandbox.driver_xreal:schematic은 기본적으로 sin_gen primitive가 xreal 타입의 출력을 직렬로 연결된 resistor primitive를 통해 구동하는 형태로 구성되어 있습니다. 4개의 driver_xreal 셀의 출력들이 하나의 노드로 short되면, 그 노드는 자연스럽게 저항 디바이더를 통해 4개 출력의 평균값을 갖게 됩니다.

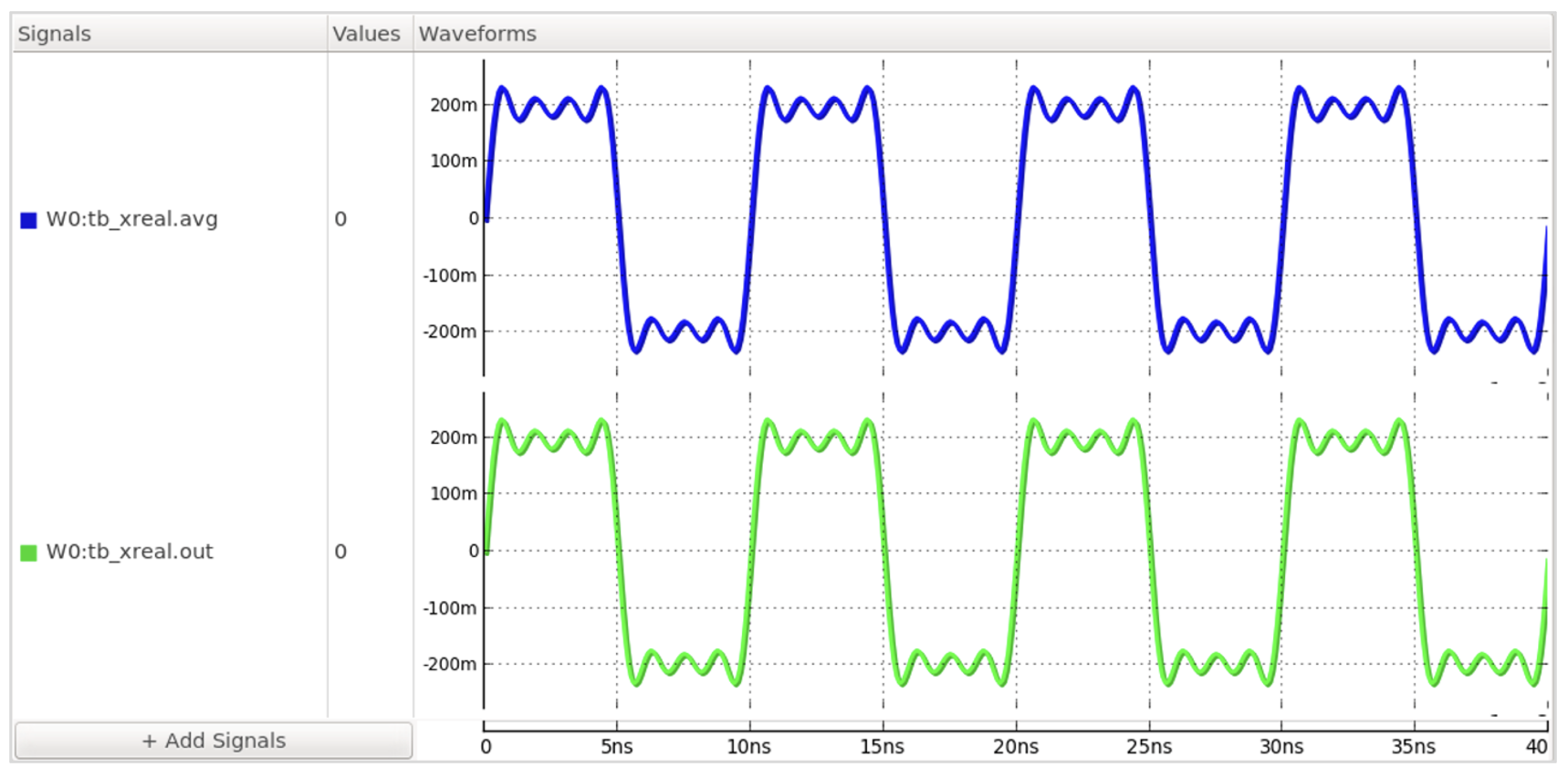

자, 아래는 이 tb_xreal 테스트벤치로 시뮬레이션한 'avg'와 'out' 신호의 파형들입니다. 이들은 앞서 보여드린, RNM nettype을 사용한 예제에서의 'avg'와 'out' 신호 파형에 각각 대응됩니다. 우선 파형이 100% 정확함에 주목하세요. 게다가, 이 시뮬레이션은 time=0 시점에서 단 하나의 event 밖에 발생시키지 않기에 엄청나게 빠릅니다. 이와 같이 XMODEL은 다양한 아날로그 회로 효과를 모델링하고, 이들을 SystemVerilog 상에서 효율적으로 시뮬레이션하기에 간단하면서도 매우 효과적인 방법을 제공합니다.

Please login or Register to submit your answer