DLL_ChargePumpDLL4DOwithReplica_ReplicaDLL : A replica delay-locked loop supporting wide-frequency-range operation of a delay-locked loop (DLL)

A replica delay-locked loop (DLL) assists the core DLL by adjusting the delay range of its VCDL with the input clock period and keeps the core DLL free from false lock issues over a wide range of input clock frequency.

This replica DLL is another type-I charge-pump DLL by itself, employing a shorter-delay VCDL made with an identical delay element with those used in the core VCDL. This shorter delay of the replica VCDL makes the replica DLL less prone to false lock issues, while its voltage-to-delay characteristic maintains a constant ratio with that of the core VCDL. The replica DLL adjusts the control voltage vctrl1 so that the delay of the replica VCDL locks to a fraction of the input clock period. The resulting vctrl1 serves as a coarse-tuning voltage for the core DLL, which adjusts its delay range according to the input clock period.

This replica DLL model is composed of a XOR-gate phase detector (PD), a charge pump loop filter (CP) with skewed up/down currents, and a replica delay element serving as the VCDL. With the CP’s up/down currentsskewed at 3:1 ratio, the delay of the replica VCDL locks to 1/8 of the input clock period.

Ref: Y. Moon, J. Choi, K. Lee, D.-K. Jeong, M. Kim, “An All-Analog Multiphase Delay-Locked Loop Using a Replica Delay Line for Wide-Range Operation and Low-Jitter Performance,” IEEE J. Solid-State Circuits, March 2000.

Input/Output Terminals

| Name | I/O | Type | Description |

| vctrl1 | output | xreal | output control voltage |

| clk_in | input | xbit | input clock |

Parameters

| Name | Type | Default | Description |

| vctrl1_init | real | 0.5 | initial value of vctrl1 (V) |

| vctrl2_bias | real | 0.5 | bias value of vctrl2 (V) |

List of Children Cells

| BLK_ChargePumpLoopFilter : A loop filter for charge-pump PLL |

| BLK_DelayElement2C : A variable delay element with dual control inputs and linear V-to-D characteristics |

| PDC_XorGatePD : A phase-only detector with an exclusive-OR gate |

List of Testbenches

| tb_check : A testbench for checking the basic operation of a replica delay-locked loop |

tb_check : A testbench for checking the basic operation of a replica delay-locked loop

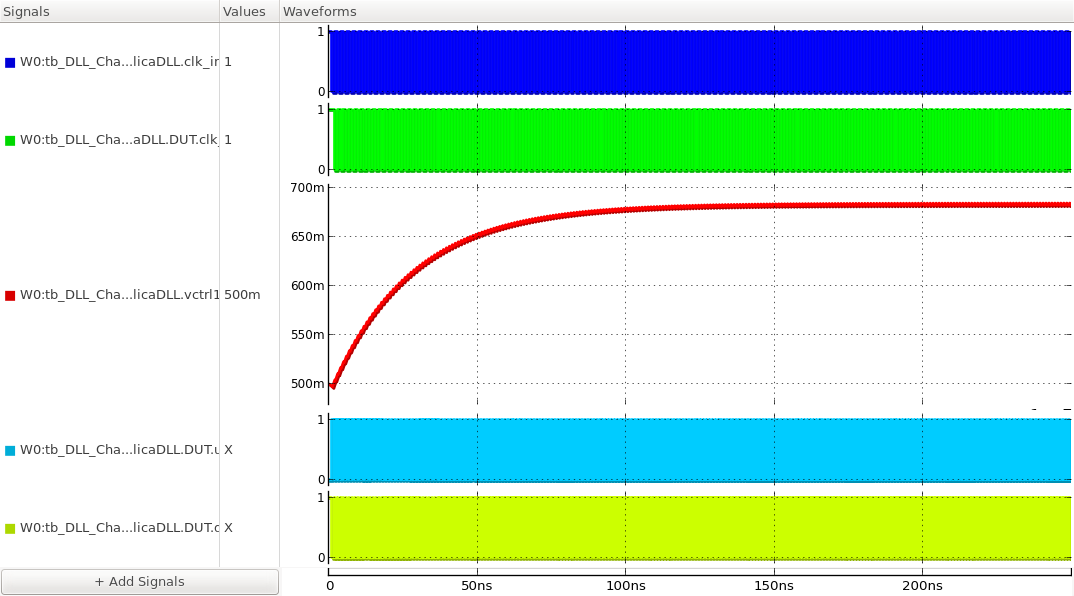

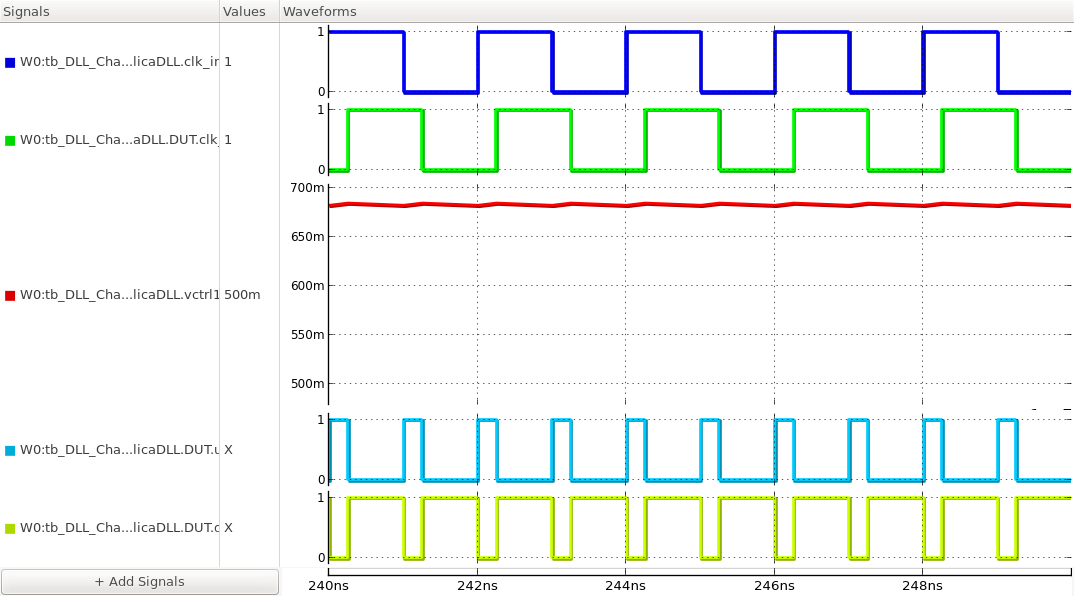

This testbench checks the basic functionality of a replica delay-locked loop (DLL), locking the delay of its replica VCDL to a fraction of the input clock period. The testbench applies a fixed-frequency input clock to the DLL and observes the locking transient of the control voltage and the final input-to-output delay at steady states.

Simulation Results

Figure. locking transient of the replica delay-locked loop.

Figure. input and output clocks of the replica delay-locked loop at steady states.