PDC_SidiropoulosPD : A precharge-type phase-only detector by S. Sidiropoulos

This precharge-type phase-only detector (PD) compares the timings of the two input clocks, clk_ref and clk_fb, and expresses their difference with the pulsewidths of the two outputs up and dn. While its operation may look similar to that of a linear phase-frequency detector (PFD), it is only capable of measuring the phase difference, and not the frequency difference, due to the lack of internal state. This PD implemented with precharge gates was proposed by S. Sidiropoulos, et al. in his paper titled, “Adaptive Bandwidth DLLs and PLLs using Regulated Supply CMOS Buffers,” published at the Symposium on VLSI Circuits in 2000. Compared to the prior precharge-type PDs, it has an advantage that the delay inserted between the master and slave stages eliminates dead zone.

This precharge-type PD model describes the precharge gates with switch primitives, which turn on and off as controlled by the xbit-typed inputs clk_ref and clk_fb. The buf_xbit and inv_xbit primitives inserted between the precharge gates add the necessary delays and produce the xbit-type outputs up and dn. These XMODEL primitives can also process accurate timings of digital pulses without being limited by the simulation timestep.

Input/Output Terminals

| Name | I/O | Type | Description |

| dn | output | xbit | dn output |

| up | output | xbit | up output |

| clk_fb | input | xbit | feedback clock |

| clk_ref | input | xbit | reference clock |

Parameters

| Name | Type | Default | Description |

| Ron | real | 0.01 | on-resistance of switches |

| Cp | real | 10f | capacitance on precharged nodes |

| delay | real | 10p | delay inserted between master and slave stages |

List of Testbenches

| tb_check : A testbench for checking the basic operation of a phase detector (PD) |

| tb_meas_tfdc : A testbench for measuring the phase error vs. net output pulsewidth transfer characteristics of a phase detector (PD) |

tb_check : A testbench for checking the basic operation of a phase detector (PD)

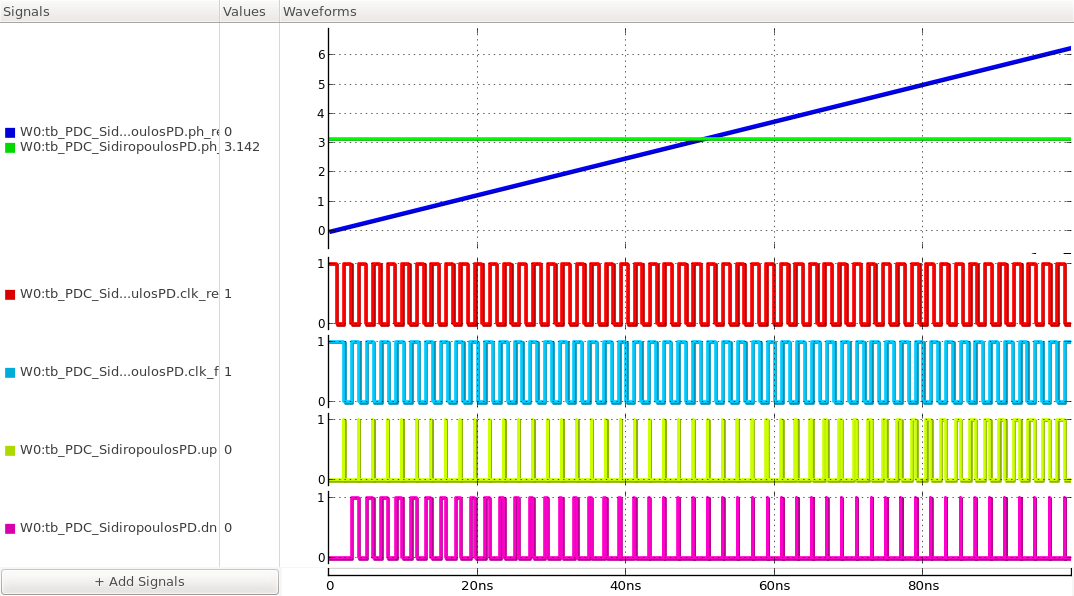

This testbench checks the basic functionality of a phase detector (PD) by applying the equal-frequency clocks to its inputs clk_ref and clk_fb, of which phase difference gradually varies from -pi to +pi radians. The net pulsewidth of the PD outputs up and dn indicates the timing difference between the two input clocks.

Simulation Results

Figure. input and output waveforms.

tb_meas_tfdc : A testbench for measuring the phase error vs. net output pulsewidth transfer characteristics of a phase detector (PD)

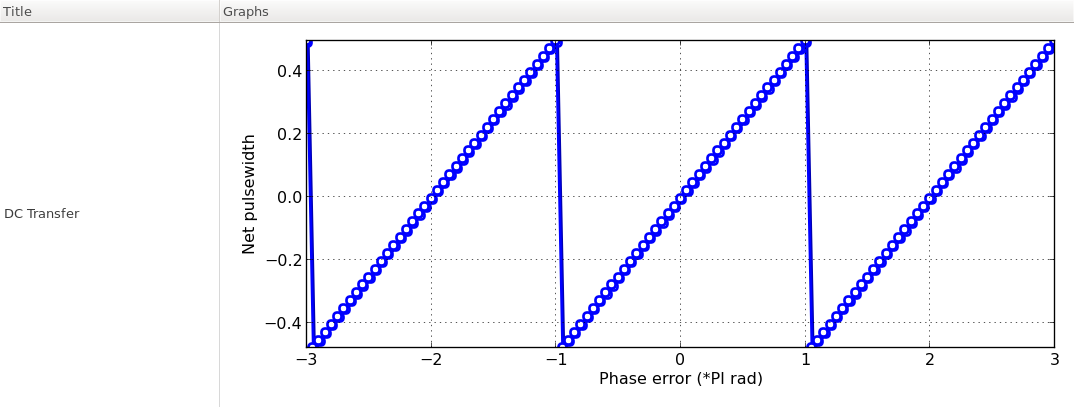

This testbench measures the phase error vs. net output pulsewidth transfer characteristics of a phase detector (PD). The testbench is configured with a probe_dc primitive, which gradually varies the phase difference between the two input clocks clk_ref and clk_fb from -3*pi to 3*pi radians and measures the net pulsewidth difference between the outputs up and dn.

A phase-only detector (PD) is expected to exhibit a transfer characteristic of which net output pulsewidth scales linearly with the phase error.

Simulation Results

Figure. input-to-output transfer characteristics of the phase detector.