DIV_SyncDividerBy16 : A synchronous divide-by-16 frequency divider

A frequency divider produces an output clock with a frequency that is equal to a divided value of the input clock frequency. A synchronous frequency divider can be realized as a synchronous counter, where all of its flip-flops are triggered by the same clock. Since its final output clock is aligned to the input clock with a short latency (i.e the clock-to-q delay of a single flip-flop), it is favored in timing-sensitive, low-noise applications. However, its tight timing constraints may make it difficult to achieve high-speed operation and low-power consumption, compared to the asynchronous frequency divider.

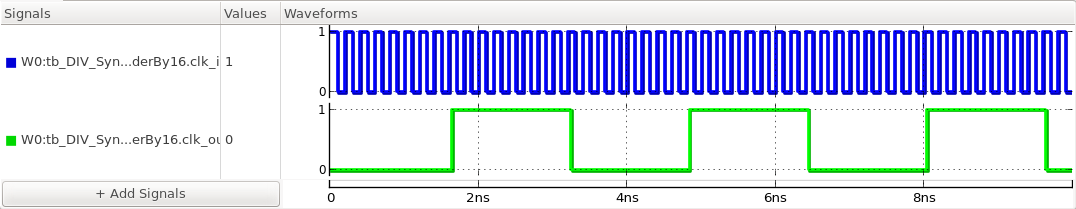

This model describes a synchronous divide-by-16 frequency divider using a set of D-flipflops updating a 4-bit value div at each rising edge of the input clock in. The parameter delay_cq defines the clock-to-q delay of each flip-flop. Since the inline primitive contains a Verilog code that increments this 4-bit value each input cycle, its MSB div can produce a divided-by-16 output clock out. The use of dff_xbit and buf_xbit primitives is for preserving the accurate timing relationship between the input clock in and output clock out, independent of the simulation timestep.

Input/Output Terminals

| Name | I/O | Type | Description |

| out | output | xbit | divided output clock |

| in | input | xbit | input clock |

Parameters

| Name | Type | Default | Description |

| delay_cq | real | 40p | clk-to-q delay of each flip-flop |

List of Testbenches

| tb_check : A testbench for checking the basic operation of a frequency divider with a fixed-frequency clock input |

tb_check : A testbench for checking the basic operation of a frequency divider with a fixed-frequency clock input

The testbench checks the basic functionality of a frequency divider by applying a fixed-frequency clock to its input in. The frequency divider is expected to produce an output clock of which frequency is a divided value of the input frequency.

Simulation Results

Figure. input and output waveforms.