DIV_ProgDividerSyncRetimer : A programmable frequency divider with a synchronous retimer

A programmable frequency divider produces an output clock with a frequency that is equal to the input clock frequency divided by a programmable factor. As it may be difficult for such a programmable frequency divider to guarantee low-latency, low-jitter output, a synchronous retimer flip-flop triggered by the input clock is commonly added to the output in order to reduce the latency and improve the jitter sensitivity.

This model for a programmable frequency divider with a synchronous retimer is described as a Verilog model followed by a dff_xbit primitive. The Verilog model describes the programmable frequency divider part and the dff_xbit primitive describes the synchronous retimer, aligning the timing of the output clock to that of the input clock. The parameter N sets the frequency division factor, which must be greater than 1. Note that the output clock’s duty cycle may not be exactly at 50% when the division factor is an odd number. For instance, when division factor is 3, the duty cycle is 33.3%. The parameter delay_cq defines the clock-to-q delay of the retimer flip-flop. The dff_xbit primitive preserves the accurate timing relationship between the input clock in and output clock out, independent of the simulation timestep.

`include "xmodel.h" module DIV_ProgDividerSyncRetimer #( parameter N = 2, // frequency division factor parameter real delay_cq = 40e-12 // clk-to-q delay of retimer )( `input_xbit in, // input clock `output_xbit out // divided output clock ); // variables integer count = 0; bit in_bit, div_bit; xbit div; // check div_factor initial begin if (N < 2) begin $xmodel_error("The division factor N should be larger than one: ", N); $finish; end end // count edges xbit_to_bit in_to_bit(.in(in), .out(in_bit)); always @(posedge in_bit) begin count = count + 1; if (count == N/2) begin div_bit = 1; end else if (count == N) begin div_bit = 0; count = 0; end end // retiming the final output bit_to_xbit div_to_xbit(.in(div_bit), .out(div)); dff_xbit #(.delay_cq(delay_cq)) dff(.d(div), .q(out), .clk(in)); endmodule

Input/Output Terminals

| Name | I/O | Type | Description |

| in | input | xbit | input clock |

| out | output | xbit | divided output clock |

Parameters

| Name | Type | Default | Description |

| N | integer | 2 | frequency division factor |

| delay_cq | real | 40e-12 | clk-to-q delay of retimer |

List of Testbenches

| tb_check : A testbench for checking the basic operation of a frequency divider with a fixed-frequency clock input |

tb_check : A testbench for checking the basic operation of a frequency divider with a fixed-frequency clock input

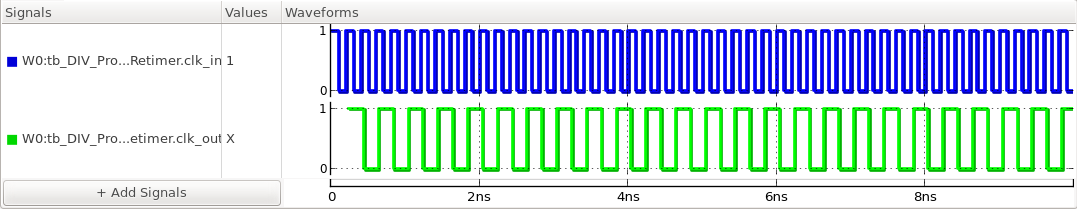

The testbench checks the basic functionality of a frequency divider by applying a fixed-frequency clock to its input in. The frequency divider is expected to produce an output clock of which frequency is a divided value of the input frequency.

Simulation Results

Figure. input and output waveforms.