Overview

GLISTER is a graphical user interface (GUI) for XMODEL and MODELZEN integrated into the Cadence® Virtuoso® Design Environment. With GLISTER, you can easily compose analog models in schematic forms, run XMODEL simulations without writing any codes, and auto-generate models from Cadence® Virtuoso® schematics using MODELZEN just with a mouse click. Basically, GLISTER makes XMODEL and MODELZEN easier and friendlier to analog designers who prefer GUI environments to command-line environments.

Key Features of GLISTER

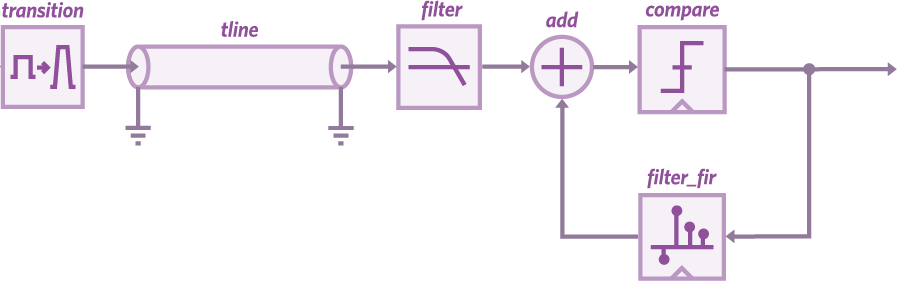

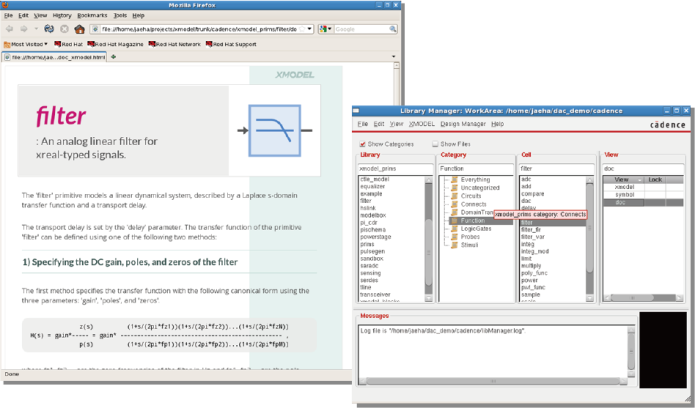

Composing Model Schematics with XMODEL Primitive Symbols

GLISTER provides the rich set of XMODEL primitives as schematic symbols and can netlist the schematics made of these primitive symbols into SystemVerilog models. Hence, composing models with GLISTER simply means placing primitive symbols on a schematic and connecting them with wires. No coding necessary! Each primitive symbol is accompanied with an on-line documentation, making the model building process more fun.

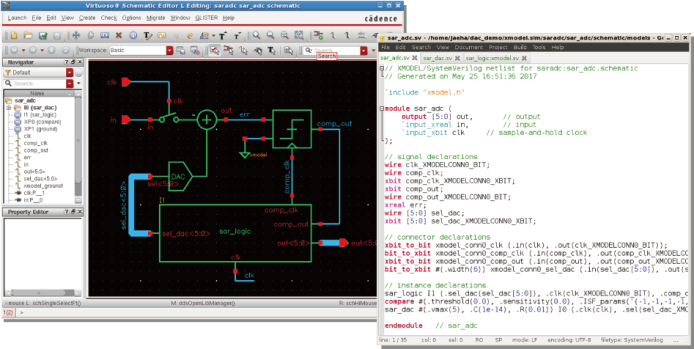

Mixed-Signal Hierarchical Netlisting

GLISTER understands that your model schematics may contain different types of signals connecting digital components as well as analog components, such as wire, real, xbit, and xreal types. When netlisting the model schematics into SystemVerilog models, GLISTER can automatically determine the proper type of each signal based on what components the signal is connected to in the design hierarchy and produce models with consistent signal types. GLISTER can also automatically insert connectors where type conversions are needed.

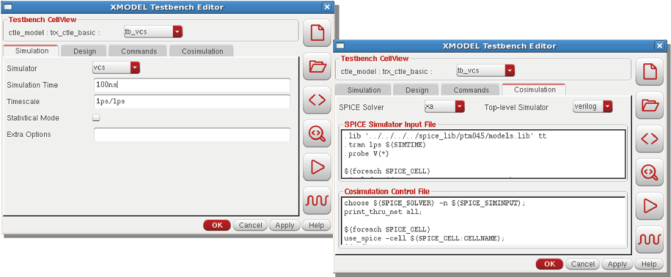

Integrated Testbench Management

With GLISTER’s Testbench Editor, you can define XMODEL testbenches as cellviews in the Cadence® design database, which specify simulation options, hierarchy configurations, additional source files, etc., using a graphical user interface. When GLISTER netlists each testbench cellview, it is exported into a simulation directory containing a Makefile and a set of source files, allowing batch processing from the command line as well.

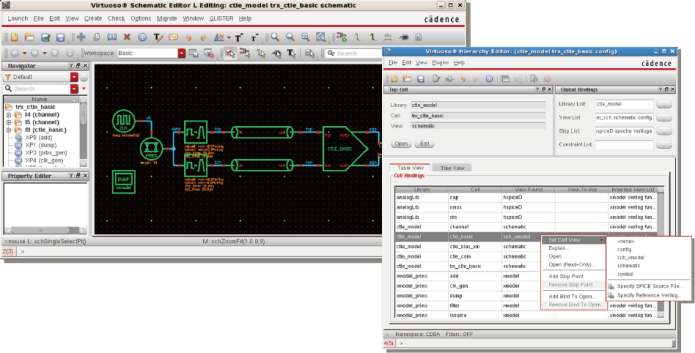

XMODEL-SPICE Co-simulation Support

When both circuit and model views co-exist in the design hierarchy, GLISTER prepares necessary files for a XMODEL-SPICE co-simulation including the SystemVerilog models, SPICE/Spectre netlists, and mixed-signal simulation control files. You can select the cellview to be used for each cell or instance using the Cadence® Hierarchy Editor. The GLISTER Testbench Editor provides a uniform interface to different simulators including Synopsys®’ VCS® and XA and Cadence®’s NCVerilog® and APS.

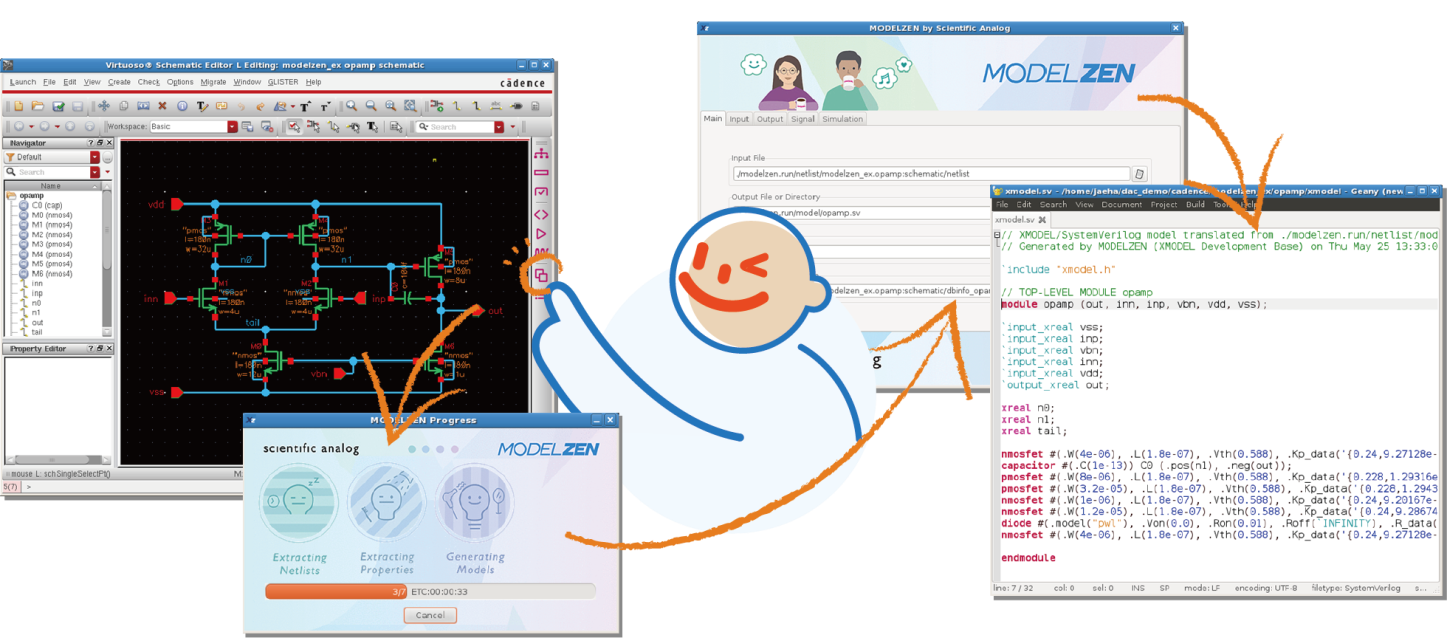

Schematic Entry Interface for MODELZEN

When you use MODELZEN within the GLISTER environment, you can auto-generate models directly from the Cadence® Virtuoso schematics just with a mouse click. GLISTER streamlines the preparation steps of model generation including netlist generation and property exporting and imports the generated models back to the design database. You can also set pin- or instance-specific properties directly on the schematics to tailor the way models are generated.